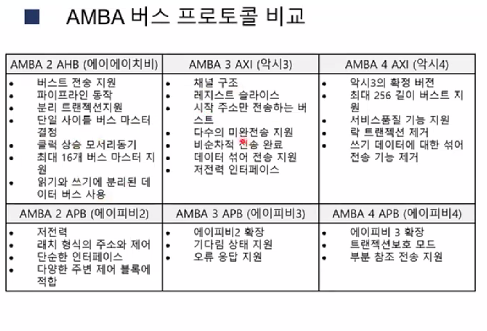

AMBA(Advanced Microcontroller BUS Architecture) busAPB, ASB, AHB, AXI, AXI-Stread 등 목적에 따라 구분된 버스들이 있음 AMBA AXI4 bus5개의 독립적인 채널로 구성되며 각 채널은 AW, W, B, AR R로 시작하는 신호 이름으로 구분AW 채널 : 쓰기 주소 전송W 채널 : 쓰기 데이터 전송B 채널 : 쓰기 결과 전송AR 채널 : 읽기 주소 전송R채널 : 읽기 데이터 전송공용 신호로 클럭(ACLK)와 초기화(ARESETn)ARESETn: 신호가 낮은 전압으로 구동할 때(통상 로직 0) 초기화ACLK: 버스 동작 기준 클럭이며 모든 버스 동작은 Rising edge에 동기 AMBA AXI4 bus채널 프로토콜vaild와 ready신호..