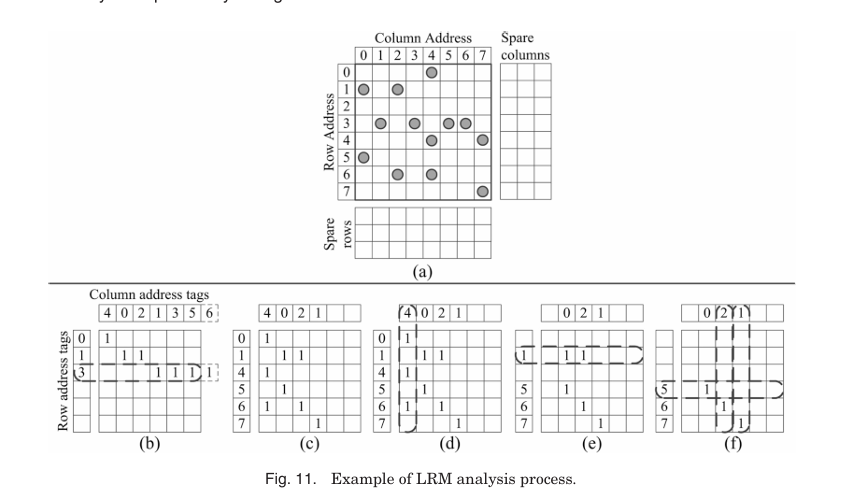

6. BIRA Techniques for 3D Memory6.1 Redundancy Scheme for 3D Memory3D memory에서는 KGD(Known-Good-Die)를 사용하며 이는 자체 포함된 Redundancy 요소로 수리된다. RA(Redundancy Analysis) 알고리즘의 성능에 따라 fixed redundancy scheme은 pre-bond와 post-bond 단계를 나누어 리던던시를 관리하지만, 사용되지 않은 리던던시가 낭비될 수 있다. 3D 메모리의 수율은 KGD에 부분적으로 의존하며, 자체 리던던시로 수리할 수 없는 메모리는 post-stacking redundancy-sharing 전략을 통해 KGD로 전환될 수 있다. pre-bond 테스트와 repair 이후 메모리..