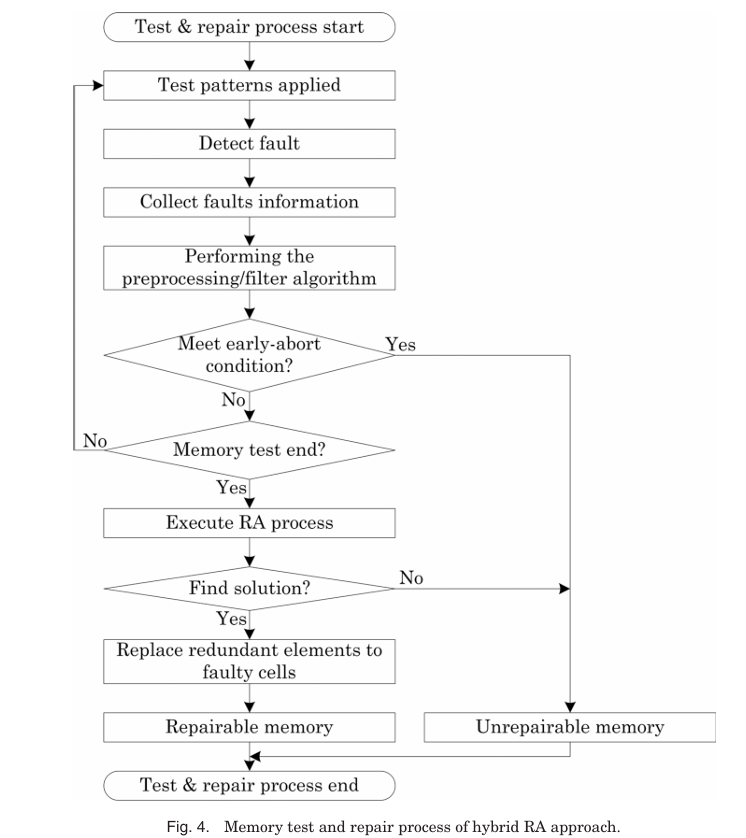

3. Repair Process and Spare Architectures3.1 Memory Repair ProcessMemory test and repair process는 hybrid RA 접근법을 통해 일반적으로 진행된다.테스트 중에 test pattern을 적용하면서 fault cell이 발견되면 해당 fault information은 나중에 수리를 위해 저장된다.Test time과 repair time을 줄이기 위해 preprocessing/filter algorithm이 적용된다. 이는 early-abort condition을 충족하는 메모리를 irreparable memory로 분류해 필터링하고 불필요한 추가 절차를 피하며 프로세스를 종료한다.Memory test가 끝난 후 RA algori..