1. Fault Model

앞서 반도체 Test Flow 에서 살펴봤던

SAF, TF, SOF, SSF Model외에 메모리에서는 아래와 같은 Fault Model 들이 있다.

1.1 Coupling Fault Model (CF)

Memory Cell에서 하나의 Cell이 다른 Cell에 영향을 주는 경우를 말한다. 일반적으로 2-Coupling Fault Model을 사용한다.

(워낙 경우의 수가 많기 때문에)

영향을 준다는 것은 예를 들어 하나의 Cell이 0에서 1로 transition하였는데 다른 하나의 Cell이 같이 0에서 1로 Transition 한 경우를 말한다.

State CF(CFst), Inversion CF(Cfin), Idempotent CF(Cfid), Linked CF 등의 형태가 있다.

1.2 Pattern Sensitive Fault Model (PSF)

1.1과 비슷한데 인접한 Cell에 의해 영향을 받는 경우를 말하는데 k-coupling faults 를 의미한다.

NPSF(Neighborhood Pattern Sensitive Faults)로 표현하는데

Type-1: 5-cell NPSF Model, Type-2: 9-Cell NPSF Model 이 있다.

아래 그림을 보면 이해가 갈것이다.

1.3 Data Retention Fault Model (DRF)

Data Loss를 의미하는데 0또는 1을 Write 한뒤 일정 시간 뒤에 다시 Read를 해보면 Write 했던 값을 유지하지 못하는 경우를 의미한다.

(Memory Cell에 따라 Default가 1이고 0이 Write 되거나, Inverting 출력인 경우도 있기 때문에 0 또는 1이다.)

주로 Leakage나 SRAM에서 Pull-up resistor가 깨진 경우 발생한다.

DRAM의 경우 주기적으로 Refresh 해주는데 이것이 잘 안되면 발생하기도 한다.

특히 노화에 따라 그 정도가 바뀌기 때문에 찾기 매우 어렵다.

1.5 기타

Dynamic Fault (Sense Amp Recovery Fault, Write Recovery Fault, Delay Fault, soft Error(SW아니다, Parametric Fault), Disturb Fault, Bridging Fault 등 다양한 Fault가 있다.

Analog 적으로 내부 0과 1을 판단하는 비교기의 threshold가 Shift 되거나 온도 전압 variation도 포함된다.

2. Test Algorithm

메모리의 경우 Logic과는 다르게 모든 Cell에 대해 0과 1을 Read/Write 하여 Test를 진행한다. 따라서 매우 많은 시간이 걸린다.

만약 삼성이나 하이닉스의 단품 메모리(DRAM, Flash 등)의 경우 위의 Fault를 모두 테스트 한다.

Embedded Memory(SoC 안에 내장된 memory)인 경우 일부 생략하기도 하기도 하지만 고신뢰성 ECU인 경우 모두 테스트를 진행해야 한다.

대표적인 메모리 테스트 알고리즘은 아래와 같다.

2.1 Zero-one Algorithm

간단하다. 0을 쓰고 0인지 읽어보고 1을 쓰고 1인지 읽어보는 것이다.

간단하지만 TF나 CF, NPSF 등은 알 수 없다.

예를 들어 2개의 Cell이 붙어있는 경우 Fault이지만 0과 1은 잘써질 것이다.

Complexity는 다른 알고리즘과 비교하기 위한 하나의 지표인데 4 Step이므로 4n이다.

여기서 n은 Memory Cell의 갯수를 의미한다.

2.1 Checkerboard Algorithm

Cell을 2개로 나눈다.(나누는 방법은 다양하다. Line by Line, or 홀짝 등)

똑같은 4-step이지만 앞서 인접한 Cell이 Short 난 경우에대해 이 알고리즘은 알 수 있다.

하지만 TF, CF는 알 수 없다.

2.2 GALPAT / Walking Algorithm

간단하게 설명하면 모든 Cell에 1을 쓰고 나서 일부의 Cell(특정한 pattern)에만 1을 쓰는데 이 1이 옮겨 다닌다고 보면 된다.

거의 모든 Fault (AF, SAF, TF, CF) 등을 검출 할 수 있지만 복잡도가 n^2 승으로 요즘같은 대용량에서 실제 사용하기에는 곤란하다.

2.3 March Test Algorithm

다양한 버전이 있는데 Memory Test의 main 알고리즘이라고 보면 된다.

설명을 위해 몇가지 예를 들면 아래와 같다.

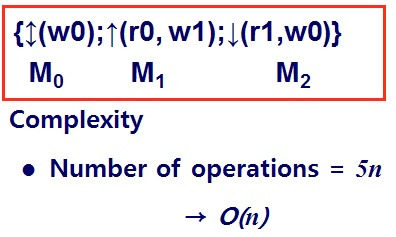

MATS+

아래와같은데 화살표 위 아래는 Address 방향이라고 보면 된다 양쪽 화살표는 Address가 상관없다고 보면 된다.

wo: 모두 0을 쓴다, r0: 0인지 읽어본다. 라는 의미이다.

예를 들어 M1 부분은 맨 아래의 Address에 대해 0인지 읽어보고 1을 쓴다음 그 다음 위쪽의 Address로 넘어가라는 의미이다.

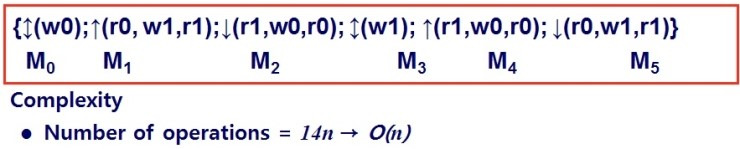

Marching 1/0 Algorithm

당연히 MATS+ 보다 복잡한 대신 많은 Fault를 검출할 수 있다.

기타 관심있으면 더 첨부파일을 읽어보고 핵심만 요약하면 아래와 같다.

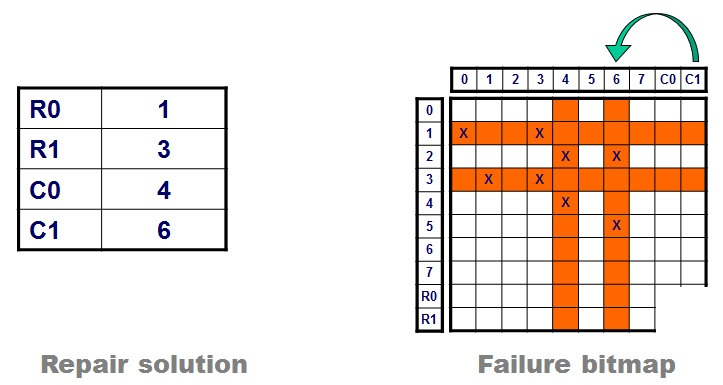

3. Built In Redundancy Analysis (BIRA)

Built In Self Repair 이라고 말하기도 한다.

메모리는 수 k부터 수 G까지 다양한 용량을 갖고 있는데 겨우 1개의 Cell에 대한 불량 때문에 버리기에는 너무 아깝고 비효율 적이다.

따라서 BIRA 개념은 약간의 불량은 Redundancy(여분의) Cell을 이용하여 고칠 수 있다.

개념만 간단히 설명하면 위와 같다.

X는 불량인 Cell이라고 보면 되고 R0, R1, C0,C1은 Redundancy Memory이다.

그림과 같이 1,3번 line을 Redundancy Memory로 대체하는 것이다.

(Address를 Redundancy 영역으로 대체한다)

이것의 핵심은 X가 너무 적은 경우 Redundancy Memory를 쓸데없는 면적으로 비용을 유발한다.

앞서 Address Mapping이나 Fault를 Repair하기 위한 별도의 알고리즘 회로가 필요하다.

단품 메모리의 경우 대부분 BIRA를 사용하며 Embedded Memory는 상황에 따라 다르다.

'DFT(Design for Testability)' 카테고리의 다른 글

| [논문 리뷰] A Survey of Repair Analysis Algorithms for Memories(1) (0) | 2025.03.28 |

|---|---|

| [논문 리뷰] An Overview of Processing-in-Memory Circuits for Artificial Intelligence and Machine Learning(DRAM PIM) (0) | 2025.03.24 |

| DFT(Design for Testability) (0) | 2025.03.20 |

| Memory Test(MBIST, LBIST, SCAN) (0) | 2025.03.19 |

| 반도체 Test Flow (0) | 2025.03.19 |