1. DFT(Desing for Testability)

Design for Testability(DFT)란 Logic의 Physical Defect를 찾기 위한 Test를 하기 위한 Test 회로를 설계하는 것을 의미한다.

Logic의 경우 단순히 입력 놓고 출력 pattern을 보면 Test가 될 거아니냐고 생각하기 쉽지만 그렇게 하면 너무 많은 경우의 수가 나오기 때문에 적절한 방법이 아니다.

게다가 수많은 Logic PIN을 다 체크하기에는 쉽지 않고 Pin, Pad 수의 제약이 따른다.

따라서 Logic의 경우 SCAN Test를 진행하게 된다.

Logic Test의 경우 정형화된 규격하에 Test 회로등이 정의 되는데 IEEE std(Standard) 1499.1 이나 IEEE std 1500이 그 예이다.

-

2. Scan Test

Logic에서 Defect를 찾아낸다는 것은 결국 모든 metal Line에 대해 Test를 진행한다는 것이다.

헌데 Combinational Logic(nand, nor, etc)의 경우에는 그냥 입력에 다양한 pattern을 주면 쉽게 알 수 있지만

Sequential Logic(Flip Flop, etc) 등의 경우는 어렵다.

왜냐하면 특정 State를 가기 위해서 앞서 State를 다시 따라가는 경우 등이 생기기 때문이다.

따라서 Sequential Logic을 Combinationalized 하면 쉽게 fault를 찾아낼 수 있으며 이것이 Scan Design이다.

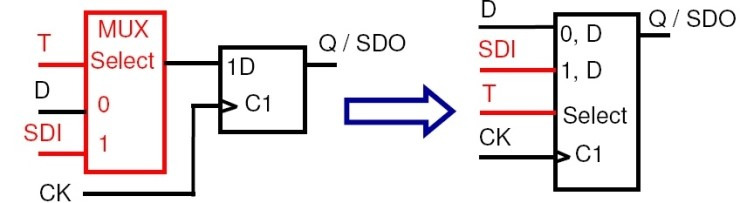

Combinationalized가 복잡한게 아니고 위와 같이 Select 신호와 함께 Mux를 추가한 DFF로 교체하는 것읻.

위의 오른쪽 그림과 같은 형태의 DFF를 Multiplexed Scan Flip-Flop 라고 하는데,

Tool에서 자동적으로 교체해준다.

(물론 일부 D-FF의 경우 안될 수 도 있는데 이러한 경우 Test Coverage를 보며 수작업으로 Design 해주어야 한다.)

DFF를 교체하고 나면 위의 그림의 오른쪽 처럼 구성할 수 있다.

이때 보면 모든 FF(Flip Flop)이 MUX를 통해 Shifted Register 처럼 Serial로 한대 묶여 있는 것을 볼 수 있다.

(이를 Scan Chain이라 한다)

이상태에서 Scan Test하는 방법은 다음과 같다.

우선 Test Mode로 Mux를 선택하고 Scan in(Serial Data Input, SDI 라고 일반적으로 예기한다.)을 통해 모든 F/F에 Test Pattern을 입력한다.

이러한 경우 F/F에 저장된 Test Pattern이 병렬로 Combinational Logic을 통과한다.

그 다음은 Test Mode를 풀고 Normal Mode로 동작시킨다.(1 Clock 동작한다는 의미이다.)

이러면 Combinational Logic의 출력이 F/F에 병렬로 저장되게 된다. 병렬로 FF에 FF값이 combinational circuit에 들어가 처리된 후 병렬로 다시 FF에 저장되는 것이다.

만약 Defect 등이 있는 경우 입력 pattern에 대해 잘못된 출력이 F/F에 저장되어 있을 것이다.

마지막으로 저장되어있는 출력 Data를 Test Mode로 Mux를 제어하여 Serial 로 출력을 내보내게 된다. 이렇게 출력을 검사하여 출력이 정상적으로 나오는지 확인한다.

이러면 단지 Clock, SCAN IN(SDI), SCAN OUT(SDO), MODE 4-Pin으로 거의 대부분의 logic에 대한 Fault를 검출해준다.

(일반적으로 Scan Clock와 Function(실제 동작시 사용하는 Clock)은 따로 사용한다.

이때 SDI의 0,1 조합을 어떻게 넣느냐는 Tool이 알아서 해준다.(Tool은 맨 마지막에 설명한다.)

이에 대한 설명을 종합적으로 설명하자면 아래 그림과 같다.

ATE는 Automatic Test Equipment로 측정 장비라고 보면 된다 Test Pattern Chip에 넣어주고 그 출력등을 확인하는 장비라고 알면 된다.

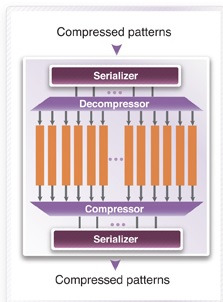

실제 SoC 측정에서 DFF 수가 적을 경우에는 상관이 없는데 DFF가 수십만 수백만게 되는 SoC에서는 이러한 측정 또한 한 세월이다.

따라서 아래 그림과 같이 Scan Chain을 여러개 구성하고(주황색 긴 막대기) Serial Data Input 이나 Output은 Decompressor와 Compressor를 통해 보다 적은 Pin을 사용하여 빠르게 처리 할 수 있다.

'DFT(Design for Testability)' 카테고리의 다른 글

| [논문 리뷰] A Survey of Repair Analysis Algorithms for Memories(1) (0) | 2025.03.28 |

|---|---|

| [논문 리뷰] An Overview of Processing-in-Memory Circuits for Artificial Intelligence and Machine Learning(DRAM PIM) (0) | 2025.03.24 |

| Memory Test(MBIST, LBIST, SCAN) (0) | 2025.03.19 |

| Memory Test(Fault Model, March, BIRA) (0) | 2025.03.19 |

| 반도체 Test Flow (0) | 2025.03.19 |