Verilog를 통한 AES 암호 설계

- AES 암호 알고리즘은 암호화, 복호화 절차로 나뉨

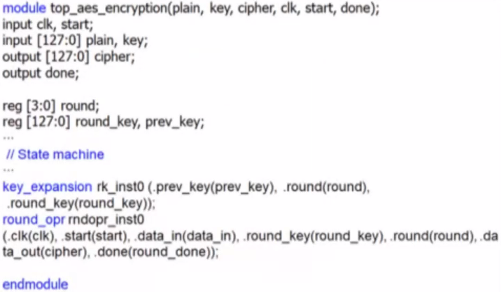

- 전체 모듈의 입력 및 출력 정보 정의 필요

- 입력: 평문(plain text) 128 비트 및 키 128 비트

- 출력 : AES-128암호화 연산 후 128비트 암호문(cipher text)

- HDL 설계 : Top module에서 평문 128비트, 키 128비트, 암호문 128비트 입출력 정의

키 확장 함수 설계

- AES 암호 알고리즘 암호화 전체 모듈 중에 부분 모듈 설계 필요

- 전체 모듈과 같이 부분 모듈과 입력과 출력을 정의

- 키 확장 회로는 입출력 관점에서만 보면 128비트 정보를 입력받아 128X10비트를 출력하는 함수

- 명세서에 정의한 수학적 표현을 해석한 후 소프트웨어 코드로 개발하고 HDL 코드로 개발

위의 수도코드를 보고 수학적으로 해석하면

- 128비트 암호키를 4개의 워드(32비트)w0,w1,w2,w3로 나눈다

- 순환(RotWord)과 치환(SubWord)연산 및 XOR 연산으로 t(j)데이터를 생성한다.(순환과 치환은 round함수로 이루어지는데 이는 다음에 살펴보자)

- XOR 연산을 반복하여 w4, ....., w43 데이터를 생성한다

- 라운드별로 생성한 키를 암호화 연산 모듈에 출력한다.

위 과정을 verilog 로 나타내면 다음과 같다

AES 암호 내 라운드 암호화 연산 설계

- 라운드함수: 128비트 라운드 입력 데이터와 128 비트 라운드 키를 입력으로 하여 128비트 라운드 출력 생성

- 라운드 함수 내 연산: 치환(subBytes), 순환(ShiftRows), 행렬곱(Mixcolumns), XOR 연산(AddRoundKey)

치환(SubBytes)연산

- 데이터를 비가역적 및 선형적으로 변환하는 절차

- S-BOX를 이용해 Look-up table 형태로 치환 변환: S-Box 변환이라고도 부름

- S-Box 변환은 8비트(1바이트)별로 독립적으로 값을 변환. 위의 테이블에 따라서 변환을 하면 됨.

- ex) 00(16진수 표현) 8비트 입력이 들어오면 63(16진수) 8비트 출력으로 치환

구현할때는 S-box 값을 모두 1대1대응으로 선언한 뒤 치환해주면 됨.

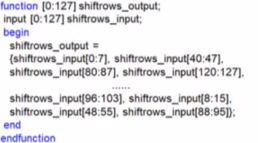

순환(ShiftRows)연산

128비트 입력을 4x4행렬로 변환 후 행에 따라 행렬을 순환하는 연산

첫번째 행은 미순환, 두번째 행은 한칸, 세번째 행은 두칸, 네번째 행은 세칸 순환 시프트 연산 수행

이를 그대로 verilog로 구현하면 됨

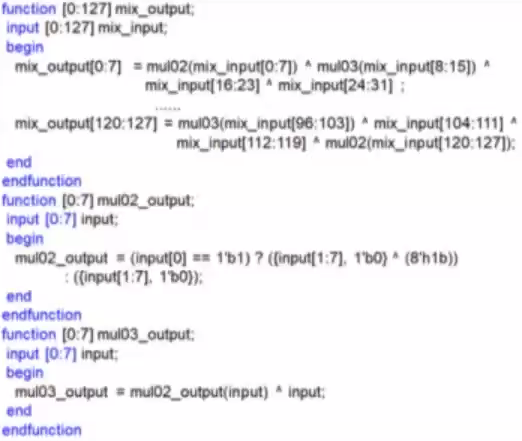

행렬곱(MixColumns) 연산

128비트 입력을 4x4행렬로 변환한 후 각 열에 행렬 곱 연산 수행

곱은 XOR을 한다는 의미임. 곱을 XOR로 생각하고 구현하면 됨.

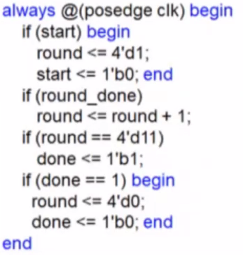

State machine 설계

- 명세서 수학적 표현과 소프트웨어 설계와 달리 HDL 코드 설계에서 가장 중요한 설계 내용

- 소프트웨어 설계 : 설계한 line 순서대로 CPU가 연산 수행

- 하드웨어 설계: 설계한 line 순서에 상관없이 하드웨어가 동시에 연산 수행

- State machine 설계하여 연산 순서가 설계자가 원하는대로 순서가 되도록 설계 필요

1) Start 신호를 통하여 암호화 연산 시작

2) 10라운드까지 연산 수행

3) 10라운드 연산 종료 후 연산 종료(done)신호 발생

4) 암호화 연산 대기 상태(idle)로 돌아감.

- State machine을 구현하면 다음과 같다. 이를 아까의 Top module에 넣어야 한다.

- State machine 설계한 것을 바탕으로 AES 암호 전체 HDL 코드 설계

- ROUND 상태에 따라 연산 및 연산 종료 결정하도록 State machine 설계

- State에 따라 AES 암호가 원하는 치환, 순환 등의 연산 수행

'AI System Semiconductor' 카테고리의 다른 글

| 13.2 디지털 회로 가속 설계(파이프라이닝, FIR(Finite impulse resonse)) (0) | 2025.01.14 |

|---|---|

| 13.1 정적 타이밍 분석(STA), 동적 규율(Dynamic Discipline) (0) | 2025.01.14 |

| 12.2 Security Chip 주요 요소 기술 (0) | 2025.01.10 |

| 11.1 Hardware Security IP (0) | 2025.01.10 |

| 10.1. AI 가속기 설계 기술 (0) | 2025.01.09 |