F,G,H 각 조합 회로의 전파 지연은 15ns, 20ns, 25ns라 하자.

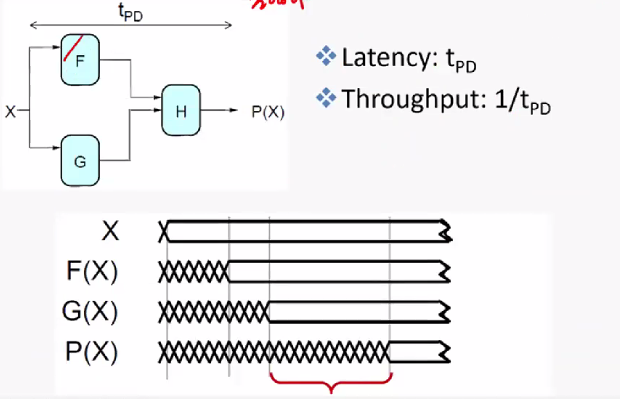

위는 파이프라이닝을 사용하지 않은 회로

- F와 G가 모두 안정된 출력을 내게되는 20ns이후 H는 유효한 연산을 할 수 있으므로 이 회로의 Latency는 20ns+25ns= 45ns임.

- H의연산이 종료된 후에 새로운 X를 인가할 수 있으므로 처리량(Throughput)은 초당 1/45ns

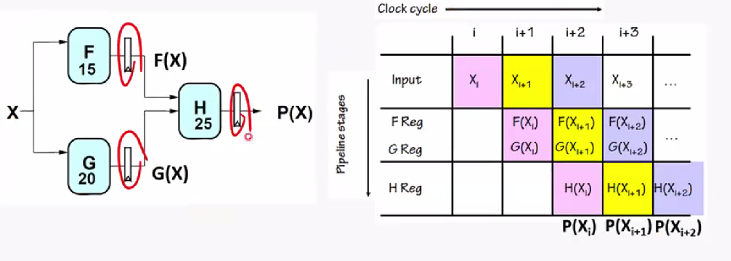

위는 2-stage 파이프라이닝을 활용한 회로임

- 레지스터의 셋업타임과 지연시간은 0ns이고 클럭 신호의 불확실성이 없다 해보자.

- 셋업타임 조건식에서 t(pcq), t(setup), t(skew)는 모두 0이므로 클럭의 최소 주기는 t(pd)로 설정할 수 있다

- F,G,H 중 최장 경로를 결정하는 조합회로는 H이므로 클럭의 주기는 25ns임.

- 이러면 주기는 25ns, Latency는 50ns, 처리량(throughput)은 1/25ns가 된다.

파이프라이닝 기법 회로 적용 방법

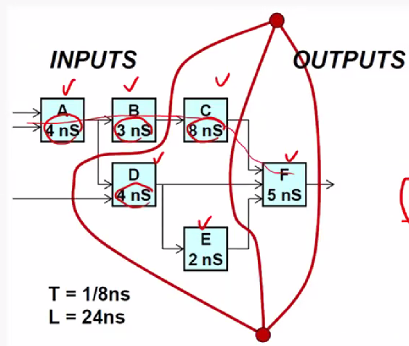

A~F까지 조합회로로만 구성된 호로를 이용하여 처리량 증가를 위해 파이프라이닝 레지스터를 삽입하는 과정을 보자

이 회로의 최장경로: A-B-C-F로 latency는 20ns, throughput: 1/20ns

파이프라인 레지스터를 어디에 넣어야 할까?

1) 회로에서 출력 선을 통과하는 선을 귿고 양 끝점을 터미널 포인트로 정한다.

2) 1단계에서 정한 두개의 터미널 포인트를 통과하는 새로운 선을 그린다. 이때 선과 회로의 교차점에서 신호의 흐름은 정방향이어야 한다

3) 이 선과 회로의 모든 교차점에 파이프라인 레지스터를 삽입한다.

- 2단계에서 선을 그릴 때는 회로에서 가장 큰 지연시간을 갖는 경로, 즉 임계경로를 끊을 수 있도록 선을 그려야 Throughput을 증가시킬 수 있음

- 세계의 붉은 선을 그린 후, 선과 회로의 모든 교차점에 파이프라인 레지스터를 삽입하면,

- 입력에서 출력까지의 모든 경로에 3개의 파이프라인 레지스터가 존재하게 됨.

- 이는 3단계 파이프라이닝 회로

- 위 회로의 throughput: 1/8ns, Latency : 24ns

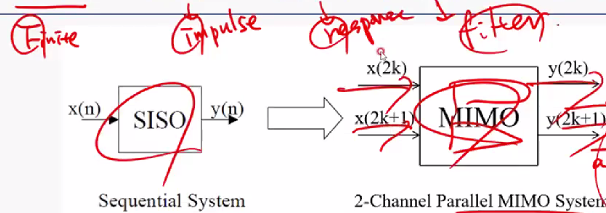

유한 임플스 응답 필터의 가속 설계 방법

SISO(Single-input single-output) : 매 클럭 주기당 하나의 샘플 x(n) 입력, 하나의 샘플 y(n) 출력하는 FIR 필터

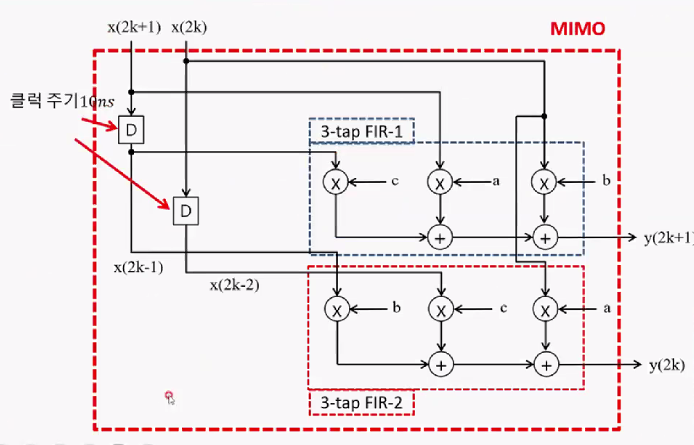

MIMO(Multiple -input Multiple-output) :두개의 채널을 이용하여 두개의 샘플을 동시에 입력받고 두개의 샘플을 동시에 출력하기 위해 FIR 필터를 병렬적으로 사용

kth 클럭 사이클에서

2개의 입력 x(2k)와 y(2k+1)d이 처리

2개의 샘플 y(2k)와 y(2k+1)이 생성

SPC는 5ns마다 입력 x(n)을 1개씩 받아서 10ns마다 출력을 2개씩 배출

2개의 FIR 필터는 10ns 클럭을 사용하며 10ns마다 출력을 2개씩 배출

PSC는 10ns마다 입력을 2개씩 받아서 5ns마다 출력 y(n)을 1개씩 배출

SPC(Serial to Parallel convertor)와 PSC(Parallel to Serial Convertor)

'AI System Semiconductor' 카테고리의 다른 글

| 15.1 시스템 버스 (0) | 2025.01.15 |

|---|---|

| 13.1 정적 타이밍 분석(STA), 동적 규율(Dynamic Discipline) (0) | 2025.01.14 |

| 12.4. AES암호 하드웨어 설계 (0) | 2025.01.10 |

| 12.2 Security Chip 주요 요소 기술 (0) | 2025.01.10 |

| 11.1 Hardware Security IP (0) | 2025.01.10 |