1.2. MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor) 소자

Transistor : 트랜지스터는 현대 전자기기의 핵심 구성 요소로, 전기 신호를 증폭하거나 스위칭할 수 있는 반도체 소자이다. 실리콘 같은 반도체 재료에 서로 다른 불순물을 주입해 여러 개의 접합부를 형성한다.

Basic transistor action:

트랜지스터는 작은 제어 신호(입력)로 큰 전류 흐름(출력)을 제어하는 방식으로 작동한다.

- Gate (게이트): 전류 흐름을 제어하는 전압 신호를 입력받는다.

- Source (소스): 전류가 시작되는 지점으로 전자를 공급한다.

- Drain (드레인): 전류가 흘러가는 끝 지점이다.

CMOS: CMOS(Complementary Metal-Oxide-Semiconductor)는 NMOS와 PMOS 트랜지스터를 결합한 회로 방식이다. 전력을 효율적으로 사용해 디지털 회로에서 많이 쓰인다.

- 전류 구동 방식의 BJT와 달리 전압 구동에 의해 소스-드레인 사이의 채널 형성

- MOSFET은 BJT에 비해 전력소모가 낮고 웨이퍼 상에서 대량 생산이 용이, 고집적화에 유리

MOSFET이 포함된 집적 회로(IC, Integrated Circuit) 칩이다. MOSFET이 회로의 기본 요소로 사용된다.

- PCB(Printed Circuit Board)에 장착된 칩의 외형을 보여준다.

- 내부에 수많은 MOSFET과 연결된 전력 및 신호 라인들이 집적되어 있다.

가운데 위 (M1~M6 레이어)

MOSFET이 포함된 반도체 소자의 금속 층(Metal Layers)과 절연 층(Oxide Layers)을 보여준다.

- M1~M6: 금속 연결 레이어로, 소자 간 신호를 전달한다. M1은 가장 아래에 있는 첫 번째 금속층이고, M6은 상위 금속층이다.

- Oxide: 금속층 사이의 절연 물질로, 소자 간 전기적 간섭을 막아준다.

오른쪽 위 (FEOL과 MOL)

MOSFET의 제조 공정에서 FEOL (Front-End of Line)과 MOL (Middle of Line) 레벨을 구분한 단면 이미지다.

- FEOL: 소자의 트랜지스터 레벨로, 실리콘 웨이퍼 위에 NMOS/PMOS 트랜지스터를 형성한다.

- MOL: 소자와 금속층 사이의 접점(Contact Metal Level)을 구성하는 단계이다.

왼쪽 아래 (패키징 단면도)

MOSFET이 포함된 IC 칩의 패키징 구조를 보여준다.

- Encapsulation: 칩을 보호하기 위해 에폭시로 Encapsulation된 부분이다.

- 1st Level Interconnection: 칩과 패키지 기판 사이의 전기 연결이다.

- 2nd Level Interconnection: 패키지 기판에서 PCB로의 연결을 나타낸다.

- FR4 PCB: PCB 기판의 일반적인 재료로 사용되는 FR4 섬유 강화 플라스틱이다.

오른쪽 아래 (NMOS 구조 단면)

NMOS 트랜지스터의 단면을 보여주는 이미지다.

- Gate: MOSFET의 전류를 제어하는 전압을 입력하는 부분이다.

- Source & Drain: 전류가 시작되고 끝나는 단자이다.

- Si (실리콘): MOSFET이 형성된 기본 반도체 물질이다.

- 20 nm: 소자의 크기 척도를 보여주며, 이 MOSFET의 게이트 길이는 20nm임을 나타낸다

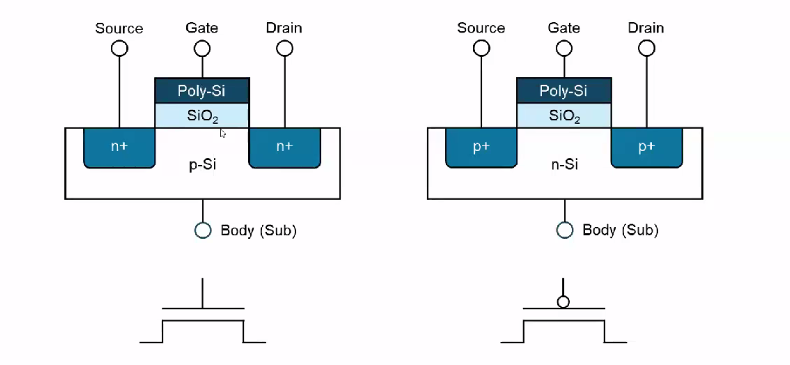

MOSFET의 구조 및 구분

n형(p-Si 기판, NMOS에서 사용됨)

- 정의: n형 반도체는 전자를 주요 캐리어로 사용하는 반도체이다.

- 실리콘(Si)에 5가 원소(예: 인(P), 비소(As))를 도핑해 생성된다.

- 도핑된 원소는 실리콘보다 전자를 하나 더 가지고 있어 자유 전자를 제공한다.

- 이 자유 전자들이 전류를 운반하는 주요 역할을 한다.

- NMOS의 p형 기판과의 관계:

- NMOS는 p형 기판 위에 n+ 소스와 드레인을 형성한다.

- 게이트에 양전압을 인가하면 p형 기판에 자유 전자가 모여 n형 채널이 형성되고, 이 채널을 통해 소스에서 드레인으로 전류가 흐른다.

p형(n-Si 기판, PMOS에서 사용됨)

- 정의: p형 반도체는 양공(hole)을 주요 캐리어로 사용하는 반도체이다.

- 실리콘(Si)에 3가 원소(예: 붕소(B), 알루미늄(Al))를 도핑해 생성된다.

- 도핑된 원소는 실리콘보다 전자가 하나 부족하여 양공(hole)을 생성한다.

- 이 양공은 전자의 빈자리로, 전자가 이동할 때마다 새로운 양공이 생기며 전류가 흐르게 된다.

- PMOS의 n형 기판과의 관계:

- PMOS는 n형 기판 위에 p+ 소스와 드레인을 형성한다.

- 게이트에 음전압을 인가하면 n형 기판에 양공들이 모여 p형 채널이 형성되고, 이 채널을 통해 드레인에서 소스로 전류가 흐른다.

NMOS (n-channel MOSFET)

- 구조:

- 기판: p형 (양공이 기본 상태)

- 소스/드레인: n+ (자유 전자가 많음)

- 게이트에 양전압을 가하면 n형 채널이 생성되어 소스에서 드레인으로 전류가 흐름.

- 특징:

- 전자의 이동 속도가 빠르므로 NMOS는 PMOS보다 더 빠르게 작동.

- 디지털 회로에서 로직 0(LOW)을 구현하는 데 사용.

PMOS (p-channel MOSFET)

- 구조:

- 기판: n형 (자유 전자가 기본 상태)

- 소스/드레인: p+ (양공이 많음)

- 게이트에 음전압을 가하면 p형 채널이 생성되어 드레인에서 소스로 전류가 흐름.

- 특징:

- 양공의 이동 속도가 느려서 NMOS보다 상대적으로 느림.

- 디지털 회로에서 로직 1(HIGH)을 구현하는 데 사용.

MOSFET의 동작: 문턱전압

게이트 전압이 특정 전압보다 높아지면 전류가 흐를 수 있는 채널이 형성되며, 이 전압을 문턱전압이라 함.

문턱전압은 MOSFET이 구동되는 시작점으로써 ON/OFF를 결정하는 임계 게이트 전압임.

그림 (a): V(GS) < V(T)

- 상태: 게이트-소스 전압 V(GS)가 문턱전압 V(T)보다 낮은 경우.

- 이 상태에서는 게이트 아래에 space charge region(공간 전하 영역)만 존재하며, 채널이 형성되지 않는다.

- 소스(Source)와 드레인(Drain) 사이에 전도 경로가 없어 전류 I(D)는 흐르지 않는다.

- 드레인에 작은 전압 V(DS)가 인가되어도 전류 흐름은 거의 없거나 무시할 정도로 작다.

그림 (b): V(GS) > V(T)

- 상태: 게이트-소스 전압 V(GS)가 문턱전압 V(T)보다 높은 경우.

- 게이트에 인가된 전압에 의해 반전층(Induced Electron Inversion Layer)이 형성된다.

- 이 반전층은 n형 성질을 가지며, 소스와 드레인 사이에 전류 경로를 제공한다.

- 소스에서 드레인으로 전류 I(D)가 흐르기 시작하며, 드레인에 전압 V(DS)를 추가로 인가하면 전류가 증가한다.

문턱전압의 의미

- 문턱전압 V(T)는 게이트에 인가해야 하는 최소 전압으로, 채널이 형성되어 전류가 흐를 수 있는 상태가 되는 시점을 의미한다.

- V(GS)가 V(T)보다 낮으면 채널이 형성되지 않아 MOSFET은 OFF 상태.

- V(GS)가 V(T)보다 크면 채널이 형성되어 MOSFET은 ON 상태.

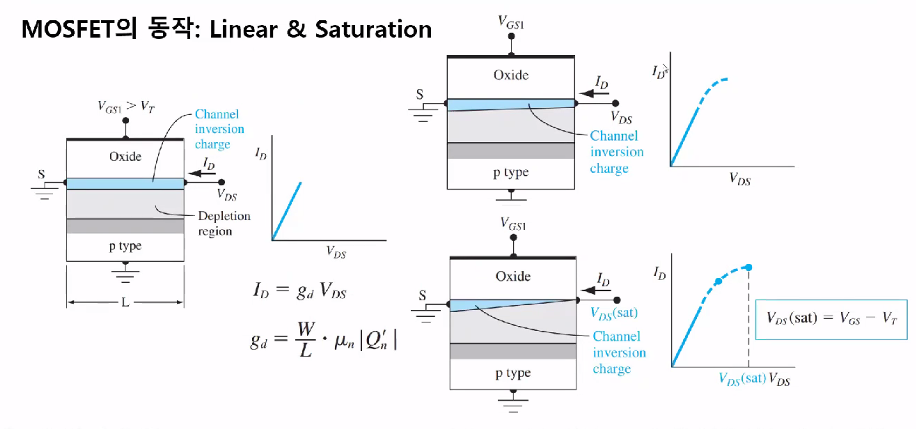

선형 영역 (Linear Region)

조건: V(GS) > V(T) 이고, V(DS) < V(GS) - V(T)

- 게이트-소스 전압 V(GS)가 문턱전압 V(T)를 초과하면, p형 기판 내에 반전층(inversion layer)이 형성되어 n형 채널이 만들어짐.

- 드레인-소스 전압 V(DS)가 작을 때, 채널 전체가 균일하게 유지됨.

- 드레인 전류 I(D)는 V(DS)에 선형적으로 비례하며, 다음과 같이 풀어서 표현됨:

- I(D) = g(d) × V(DS)

- g(d) = (W / L) × μ(n) × |Q(n)|

- W: 채널 폭

- L: 채널 길이

- μ(n): 전자 이동도 (전자 이동 속도를 나타내는 상수)

- |Q(n)|: 채널 전하 밀도 (게이트에 의한 전하량)

- 드레인 전류 I(D)는 드레인 전압 V(DS)가 증가할수록 선형적으로 증가함.

3. 포화 영역 (Saturation Region)

조건: V(GS) > V(T) 이고, V(DS) ≥ V(GS) - V(T)

- 드레인-소스 전압 V(DS)가 V(GS) - V(T)에 도달하면, 드레인 쪽 채널의 폭이 좁아지며 "pinch-off" 현상이 발생.

- 이 상태에서 드레인 전류 I(D)는 더 이상 V(DS)에 의존하지 않고, 일정한 포화 상태에 도달. 드레인 전류는 다음과 같이 풀어서 표현됨:

- I(D(sat)) = 0.5 × (W / L) × μ(n) × [V(GS) - V(T)]²

- V(GS): 게이트-소스 전압

- V(T): 문턱전압

- W: 채널 폭

- L: 채널 길이

- μ(n): 전자 이동도

- [V(GS) - V(T)]²: 게이트 전압과 문턱전압의 차이에 의해 생성된 채널 전류의 크기.

- 이 상태에서는 드레인 전류가 V(GS)와 V(T)에 의해서만 결정되고, 드레인 전압 V(DS)의 증가와 무관하게 일정함.

- 그래프에서 I(D)는 일정하게 유지된다.

왼쪽은 출력 특성(드레인 전류와 드레인 전압의 관계), 오른쪽은 전달 특성(드레인 전류와 게이트 전압의 관계)

MOSFET의 Nonideal 거동

subthreshold 전도

- 문턱전압 이하에서 드레인 전류가 흐르는 것은 약반전(Weak Inversion)상태에서 소수 캐리어의 전도에 의해 생기는 현상으로, 전력 소모로 이어짐

- 위에서 전달 특성에서 V(T)전에 전류가 이미 흐르는 것을 볼 수 있는데, 이게 subthreshold 전도임.

채널 길이 변조(Channel Length Modulation)

- 드레인 전압의 변화에 따라 공핍층 두꼐가 변화함에 의해 채널 길이가 함께 변동되는 것

- 채널의 길이가 짧아지면 공핍층 두께의 영향이 커지며 실질적인 유효채널 길이가 달라져 설계 시 예상했던 트랜지스터 전류값과 차이가 생겨 동작 오류로 이어질 수 있음

Short Channel에 따른 부작용

- Short Channel로 인해 누설전류가 생김.

- 이는 MOSFET 본연의 역할인 게이트 전압을 통한 ON/OFF 전류 상태의 제어를 어렵게 만들고, 이는 COMS 회로에서의 연산오류 등을 생기게함.

펀치쓰루

- 웨이퍼 기판 하부의 공핍층이 연결되어 발생하는 우회 전류

- 채널 길이가 과도하게 짧아지면 소스쪽과 드레인쪽의 두 공핍층이 접촉할 수 있게되고, 소스/드레인 간 전계에 의해 연결된 공핍층을 통해 누설전류가 흐르게 되어 채널 통제성을 잃어버릴 수 있음

DIBL(Drain-Induced Barrier Lowering)

채널의 길이가 짧아지면서 전계가 커지고, 이로인해 소스 단자쪽의 공핍층 두께가 감소하여 드레인 전류가 증가하는 현상

HCI(HOT Carrier Injection)

- 게이트 절연막을 통과하여 게이트 단자로 흐르는 누설 전류

- Short Channel에서 높아진 전계로 인해 에너지를 얻은 전자들이 드레인 단자 주변에서 p형 SI격자들과 충돌하여 2차, 3차 전자를 발생 -> 이때 일부 전자들이 게이트 전압에 의해 게이트 절연막 쪽으로 흘러 절연막 내 또는 계면에서 트랩 -> 문턱전압의 변동으로 이어져 게이트 전압의 통제 능력 불안정

GIDL(Gate-INduced Drain Leakage)

- 게이트 전압보다 드레인 전압이 높을 때 공핍층이 두꺼워진 드레인 단자와 게이트 단자 사이의 전압 차가 커지면서 발생하는 터널링에 의한 누설전류

- 게이트-드레인 간 전계에 의해 드레인 단자 공핍층 상부에 존재하는 EHP에 의해 발생한 전자들이 드레인의 공핍 영역을 통과해 양전압이 걸린 드레인으로 전류가 흐를 수 있음

- 소자 공성 시 게이트 단자와 드레인 단자 간 겹치는 오버래핑 영역이 커지면 GIDL 현상이 심해질 수 있음.

'AI System Semiconductor' 카테고리의 다른 글

| 2.4. 산화물 기반(Oxide-Based) 저항 변화(Resistance Change)물질 응용(OxRAM) (0) | 2025.01.06 |

|---|---|

| 2.3. 상변화(Phase change) 소재의 반도체 응용 (1) | 2025.01.06 |

| 2.2 강유전체(Ferroelectric 소재의 응용) (0) | 2025.01.06 |

| 1.4. 메모리 반도체 소자 (0) | 2025.01.06 |

| 1.3. CMOS 기술 (1) | 2025.01.06 |