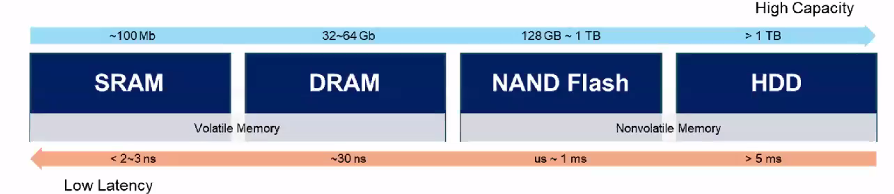

메모리의 종류

RAM(Random Access Memory) : 명령을 통해 데이터를 읽거나 쓸 수 있는 메모리. 데이터가 저장되는 주소를 통해 데이터를 자유롭게 읽고 쓸 수 있는 기억장치. 데이터를 임시 저장하는 데 사용

DRAM

- DRAM은 1개의 MOSFET과 1개의 Capacitor로 구성되어 Capacitor에 충전된 전하로 데이터 저장 상태를 구분하며, 시간에 지남에 따라 (Dynamic) 방전됨. (SRAM은 6개의 MOSFET으로 구성되어있으며, 내부 Feedback 회로를 통해 전원이 공급되는 동안 지속적으로 (Static)데이터 상태를 유지)

- 속도가 빠르고 신뢰성 우수, 주기억장치로는 대부분 DRAM 사용

- Volatile 메모리로 장시간 데이터 저장 시 전력소모 높아짐.

DRAM의 구조

WL(Word LIne) : TR의 게이트 단자에 연결되어 메모리 셀 ON/OFF/ 수행

BL (Bit Line) Data Transfer Line으로 TR의 소스 단자에 연결되어 Read/Write 수행

TR(Transistor) : 스위치용 nMOSFET으로 게이(WL)의 전압인가를 통해 BL로부터 들어오는 데이터(전류)를 전송하는 역할

Cap(Capacitor): 데이터 저장소, Cap에 축전된 전하량에 의해 데이터 상태 구분

DRAM의 동작 과정

Write : WL을 통해 특정 Address의 TR이 ON된 상태에서 BL-소스/드레인 채널-Storage Cap을 통해 전하를 충전 ㄷ또는 방전하는 방식

Write "1" : BL의 High전위를 통해 전하들이 Storage Cap으로 충전되고 Cap의 전위가 Low에서 High로 상승

Write "0" : BL의 Low전위를 통해 Storage Cp으로부터 전하들이 빠져나가고, Cap의 전위가 High에서 Low로 하강

Read : WL을 통해 특정 Address의 TR이 ON된 상태에서 High와 Low 사이의 Read Voltage(기준 전위, V(DD)/2)를 BL을 통해 인가하여 Storage Cap의 현재 상태를 알아냄.

Read "1" : High상태의 Storage Cap으로부터 전하가 일부 빠져 BL의 전위가 상승

Read "0" : Low 상태의 Storage Cap으로 전하가 일부 충전되어 BL의 전위가 하강

Read 동작은 Cap의 전하를 일부 변경시키기 때문에 Read 후 리프레시 동작이 필요.

NAND Flash 메모리

- Flash 메모리 단위 셀은 MOSFET 1개로 구성

- DRAM과 달리 리프레시가 필요 없이 데이터를 원하는 시간만큼 저장할 수 있는 비휘발성 메모리

- Flash메모리는 0 또는 1의 bit 데이터를 저장(Programming,PGM), 삭제(Erasing,ERS), 읽기(Read) 동작 등 수행

- DRAM대비 속도는 떨어지나 데이터 저장량은 훨씬 크고 데이터 업데이트가 쉬움

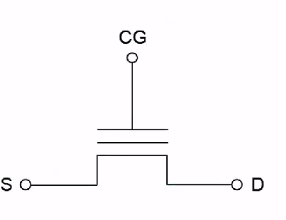

NAND Flash 메모리 구조

- 컨트롤 게이트(CG) : Cell에 전압을 인가하는 곳으로 전압의 크기와 부호에 따라 PGM, ERS, Read가 결정됨.

- Blocking Oxide(BOX) : FG에 저장된 전하의 CG로의 손실을 방지하는 절연막

- 부유(Floating) 게이트(FG) : PGM과정에 의해 TOX를 통해 주입된 전하를 저장하는 곳으로 전하가 채워져 있으면 1, ERS 과정에 의해 전하가 빠져나간 상태이면 0으로 메모리 state를 정의

- Tunneling Oxide(TOX) : CG에 인가된 전압에 의해 Substrate(Silicon, Sub)로부터 FG로 전하의 주입에 일어나는 얇은 절연막.

NAND Flash 메모리 셀의 동작

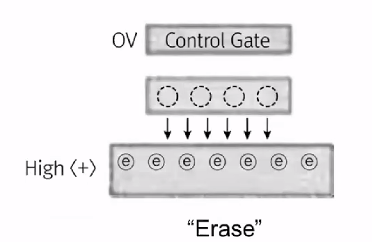

Flahs메모리 셀 내 데이터의 PGM과 ERS 과정은 CG와 Sub간의 전압 인가를 통해 FG에 전하를 주입 또는제거하는 과정

PGM : CG에 강한 양전합(High)을 인가하고 Sub을 접지시키면 전자가 터널링을 통해 Sub에서 FG로 주입됨.

FG에 전자가 주입되어 문턱전압이 양의 값을 가질 때 PGM이라 하고, 이를 상태 0이라 정의

Read : PGM 전압보다 낮은 기준 전압(Middle)을 CG에 인가하여 채널 내 흐르는 전류량을 통해 FG의 상태를 1 또는 0인지 확인. FG의 전하량에 따라 문턱전압의 차이가 생기므로 채널 전류량을 통해 FG의 상태를 확인할 수 있음.

ERS : PGM과 반대로 CG를 접지시키고 Sub에 강한 양전압을 인가하여 FG에 저장딘 전자를 Sub로 빼냄.

전자가 빠져 PGM대비 문턱전압이 음의 값으로 이동하면 ERS라 하고, 이를 상태 1이라 정의

NAND Flash 메모리 셀의 성능

- Flash 메모리 셀은 PGM/ERS 과정을 반복할수록 절연막이 열화되어 P/E Cycle 수가 제한되어 있음

- 또한 FG에 저장된 전자는 절연막을 통해 방전될 수 있어 Data 유지시간이 제한적이며, 이를 메모리의 retention 특성이라 함.

- P/E Cycle 및 Retention 특성은 셀의 신뢰성을 결정

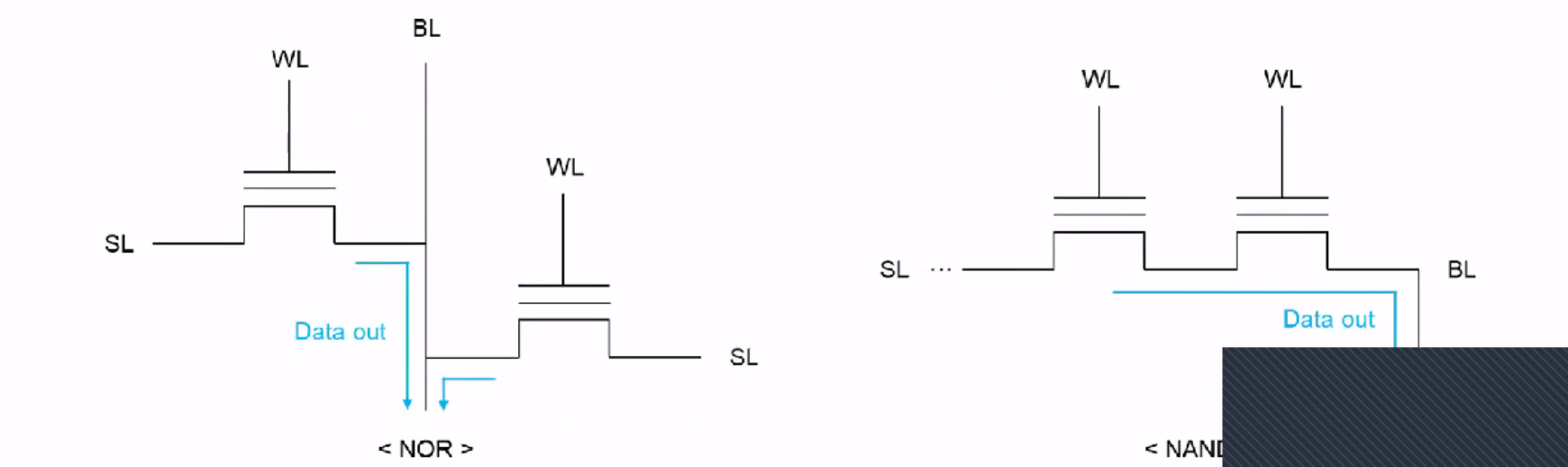

NAND Flash 메모리의 집적 구조: NOR vs NAND

- NOR : BL과 SL 사이 셀 배치가 병렬

- NAND : BL과 SL 사이 셀이 직렬 배치

응답 속도 및 면적

- NOR는 응답속도는 빠르지만 저장을 위한 면적이 넓음

- NAND는 응답 속도는 NOR대비 느리지만 필요 면적이 좁음

- NAND는 Contact 수가 적어 4F^2실 크기로 제조할 수 있고, 따라서 고집적화가 가능.

- NAND 구조가 살아남아 방대한 양의 데이터를 처리해야하는 수요가 증가하며 NAND Flash 메모리의 수요가 증가.

'AI System Semiconductor' 카테고리의 다른 글

| 2.4. 산화물 기반(Oxide-Based) 저항 변화(Resistance Change)물질 응용(OxRAM) (0) | 2025.01.06 |

|---|---|

| 2.3. 상변화(Phase change) 소재의 반도체 응용 (1) | 2025.01.06 |

| 2.2 강유전체(Ferroelectric 소재의 응용) (0) | 2025.01.06 |

| 1.3. CMOS 기술 (1) | 2025.01.06 |

| 1.2. MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor) 소자 (0) | 2025.01.06 |