1. PIM이 등장한 배경: Von-Neumann의 한계

컴퓨터를 생각하면 Von-Neumann 아키텍처가 떠오른다. 이 구조는 메모리에서 데이터를 가져와 연산 유닛에서 처리한다. 결과를 I/O 장치로 보여주는 방식이다. 수십 년간 효율적이었던 모델이다. 현대 컴퓨터 아키텍처의 기본 틀이 됐다.

하지만 새로운 애플리케이션으로 문제가 생겼다. 데이터 이동이 시간과 에너지를 많이 소모한다. 메모리 집약적인 작업에서 병목현상이 발생한다. 마지막 레벨 캐시 미스가 잦은 경우가 그렇다. DRAM에서 연산 유닛으로 데이터를 옮기는 비용이 크다. 논문에 따르면 이 에너지는 연산보다 100배 더 소모된다.

DRAM 모듈은 연산 유닛보다 낮은 주파수로 작동한다. 애플리케이션마다 메모리 요구와 접근 패턴이 다르다.

2. PIM을 가능하게 하는 Memory technologies

2.1. DRAM

DRAM 메모리 시스템은 메모리 컨트롤러, 메모리 버스, 그리고 DIMM(듀얼 인라인 메모리 모듈)으로 구성된 DRAM 디바이스로 이루어져 있다. 최신 CPU는 대부분 메모리 컨트롤러를 통합하고 있으며, DRAM DIMM과 연결된 메모리 채널을 통해 데이터를 주고받는다. DRAM은 마더보드에 별도의 슬롯을 가지고 있어서 교체나 수리가 간편하다.

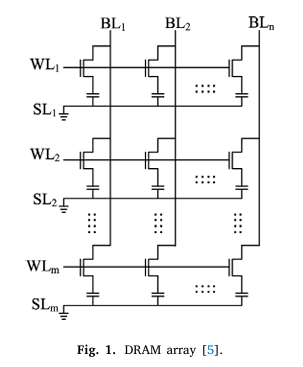

DRAM은 하나의 트랜지스터와 캐패시터로 구성된 셀에 데이터를 저장한다. 캐패시터가 충전되면 논리값 1이고, 방전되면 0이다. 셀들은 워드라인과 비트라인으로 연결된 배열 구조를 이루고 있다. 특정 행이 활성화되면 데이터가 행 버퍼로 옮겨져 CPU로 전송된다(Fig 1).

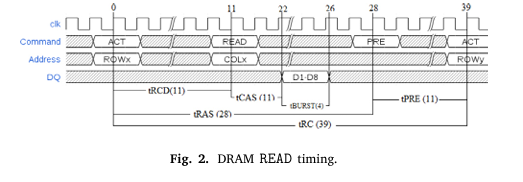

데이터를 읽으려면 ACT 명령으로 행 주소를 활성화하고, READ 명령으로 열 주소를 지정한다. 읽기 과정에서 데이터가 지워지므로, 행이 닫힐 때 데이터를 다시 써주는 PRECHARGE 작업이 필요하다(Fig 2). DRAM은 메인 메모리의 표준 기술이지만, 크기 축소로 오류에 취약해지고 핀 수 제한으로 대역폭 요구를 충족하기 어려운 상황이다.

2.2. HBM

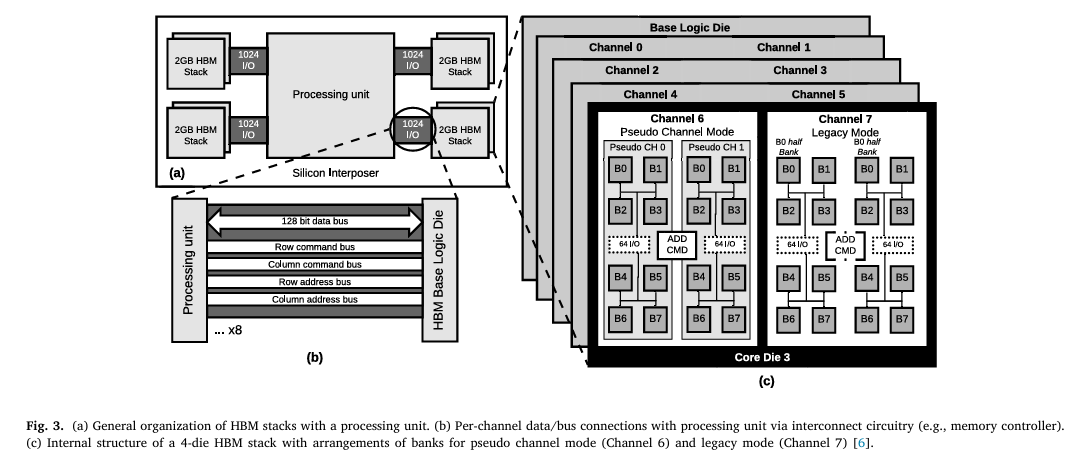

HBM은 현대 애플리케이션의 높은 대역폭을 충족하기 위해 개발된 3D 스택 DRAM이다. 여러 DRAM 다이를 base logic layer 위에 쌓아 만든 기술이다. 각 DRAM 다이는 두 개의 독립적인 채널을 가지며, HBM2에서는 이를 두 개의 pseudo-channel 로 나눌 수 있다. 여러 HBM 스택이 프로세싱 유닛과 silicon interposer 를 통해 1024비트 연결로 통신한다. DRAM 기반이지만, 독특한 구조와 넓은 데이터 연결로 높은 대역폭과 용량을 제공한다(Fig 3).

2.3. HMC

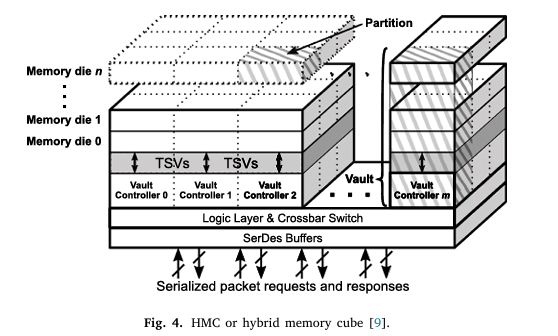

HMC는 3D 스택킹을 활용한 또 다른 DRAM 파생 기술이다. DRAM 다이가 파티션으로 나뉘어 수직으로 연결되며, 이를 vault라고 부른다. 각 vault 는 base logic layer에 있는 메모리 컨트롤러로 관리된다(Fig 4). vault controller는 고속 serialization/de-serialization circuit을 통해 패킷 기반 통신으로 다른 HMC나 호스트와 연결된다.

2.4. STT-MRAM

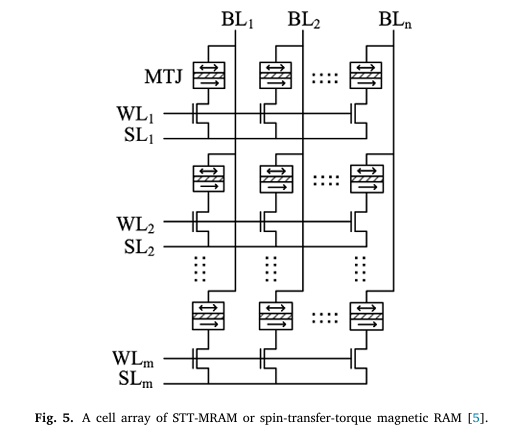

STT-MRAM은 스핀 편극 전류로 인한 자기 저항을 기반으로 한 비휘발성 메모리 기술이다. 자기 터널링 접합(MTJ)을 중심으로 데이터를 저장하고 프로그래밍한다. MTJ는 얇은 유전체 층이 두 개의 강자성 층 사이에 있는 구조이다. 두 층의 극성이 같으면 저항이 낮아 0이고, 다르면 높은 저항으로 1이다. 셀 배열 구조는 DRAM과 비슷하다(Fig 5).

2.5. ReRAM

ReRAM은 비휘발성 메모리 기술로, 금속-절연체-금속(MIM) 구조의 두 단자 셀을 사용한다. 전도성 필라멘트를 생성하거나 해제해 저항 상태를 바꾼다. SET은 저항을 낮추고, RESET은 높이며, READ는 저항 상태를 감지한다. 작은 감지 전압으로 상태를 확인하는 방식이다.

2.6. PCM

PCM은 비휘발성 메모리 기술로, 상변화 물질(ex) Ge2Sb2Te5)을 활용한다. 두 전극 사이의 물질이 결정질 또는 비정질 상태로 저항을 달리한다. SET으로 1, RESET으로 0을 설정하고, READ로 상태를 읽는다. SET 작업이 느리고, 셀 내구성이 낮아 고성능 시스템의 메인 메모리로는 부적합하다.