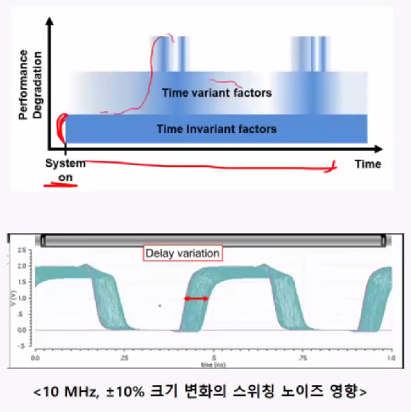

특성 변화 원인

- 시변(Time Variant)특성 변화

- 스위칭 노이즈에 의한 공급전압, 바이어스 전압 변화

- 온도 변화

- 시불변(Time Invariant) 특성 변화

- 공정(process) 산포에 의한 W, L, Vth등의 변화

- 공급전압 및 바이어스 전압 오차

문제점

- 아날로그 회로의 경우 전압 이득, 대역폭 등을 변화시킴

- 디지털 회로의 경우 타이밍에 변화를 주어 셋업 홀드 마진에 악영향

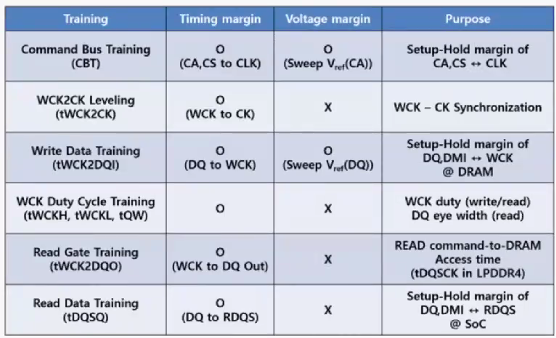

메모리인터페이스의 트레이닝

- 전압 및 타이밍 마진 확보를 위한 다양한 트레이닝을 지원함

- Command/Address 트레이닝

- Command Bus Traning

- Write Margin 트레이닝

- WCK2CK leveling

- Write Data Training

- WCK Duty Cycle Training

- Read Margin 트레이닝

- Read Gate Training

- Read Data Training

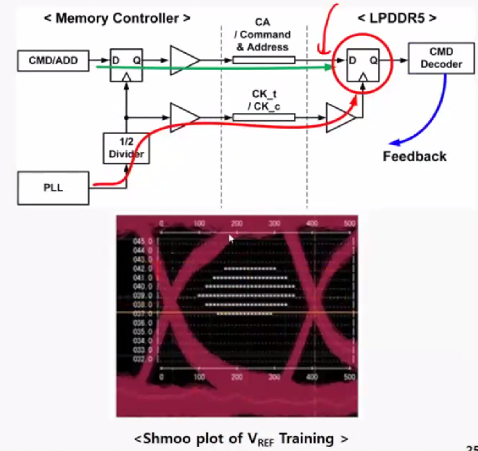

Command Bus Training(CBT)

- CA와 CK간 타이밍 마진 확보

- CA용 기준전압과 CA-CK간 위상을 변화시키면서 타이밍 마진이 가장 넓은 구간을 찾음

- 명령어 입력에 문제가 없어야하므로 DRAM 동작 시 우선적으로 수행

- 밑의 사진에서 하얀 점이 pass한 것임. 나머지는 fail. 타이밍 마진이 가장 긴 구간을 여기서 찾으면 됨

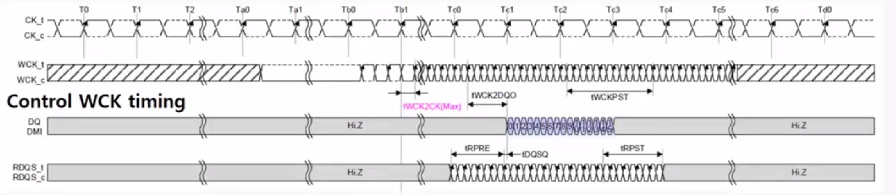

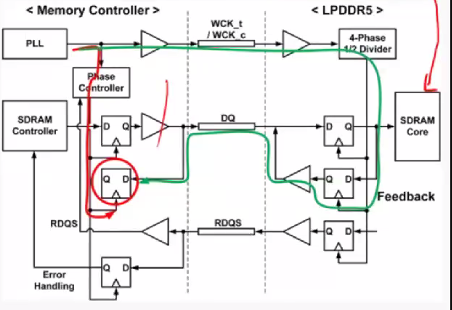

WCK2CK Leveling

- 메모리에 공급되는 서로 다른 클록 영역인 CK와 WCK 간의 타이밍 오차를 보정하는 트레이닝

- DDR 메모리 및 LPDDR3와 LPDDR4메모리에서는 Write Leveling이라고 함

- WCK에 의해 정렬된 DQ를 CK에 동기화된 쓰기 관련 컨트롤 신호와 동기화

Write Data Training

- DQ와 WCK간의 셋업/홀드 타이밍 특성(tWCK2DQI) 확보를 위한 Write Data Training

- 전압 마진 확보를 위한 V(REF) Level Training

- WCK 신호 퀄리티 확보를 위해 WCK Duty Cycle Training

- 필요한 경우 메모리 동작 중간에 주기적으로 트레이닝 시행 가능(Periodic Training) -> 시간에 따라 변하는 온도 및 전압에 의한 특성 변화를 보정

Read Data Training

- 메모리의 데이터 수신을 위한 Write Data Training과 동일한 과정을 메모리 컨트롤러의 데이터수신을 위해 수행

- 약속된 데이터를 메모리의 FIFO에 쓴 후, 다시 출력하여 메모리컨트롤러가 수신 -> 수신 결과를 바탕으로 메모리컨트롤러의 수신기의 전압 및 타이밍 마진 확보

Read Gate Training

- 다수의 메모리로부터 데이터를 읽기 위해서는 메모리의 Access Time 바탕의 스케쥴링 필요(충돌 방지)

- 여기서 Access time은 읽기 명령 시점으로부터 Read Latency 이후 데이터가 출력되기까지 시간

- Read Gate Training을 통해 tWCK2DQO 특성을 측정 및 보정함으로써 메모리 간 Access time을 관리

- DDR 메모리의 경우 메모리 내부 Delay-locked loop을 사용하여 칩마다 acces time을 관리

'AI System Semiconductor' 카테고리의 다른 글

| 9.2. DRAM Sense amplifier (0) | 2025.01.09 |

|---|---|

| 9.1. 저전력 고속 메모리 설계(CMOS 인버터) (0) | 2025.01.09 |

| 8.3. 송신회로와 수신회로 (0) | 2025.01.09 |

| 8.2. 메모리 인터페이스 (0) | 2025.01.09 |

| 7.4. AI를 위한 저전력 메모리기법(AI를 위한 압축 기법) (0) | 2025.01.08 |