카테고리 없음

Cache 메모리 설계

-운-

2025. 2. 23. 21:08

- Block size = 4B

- Memory size = 256B (64Blocks)

- Cache size = 16B(4sets)

- Write-back policy

- req & ack handshaking

- One req at a time

Verilog 코드

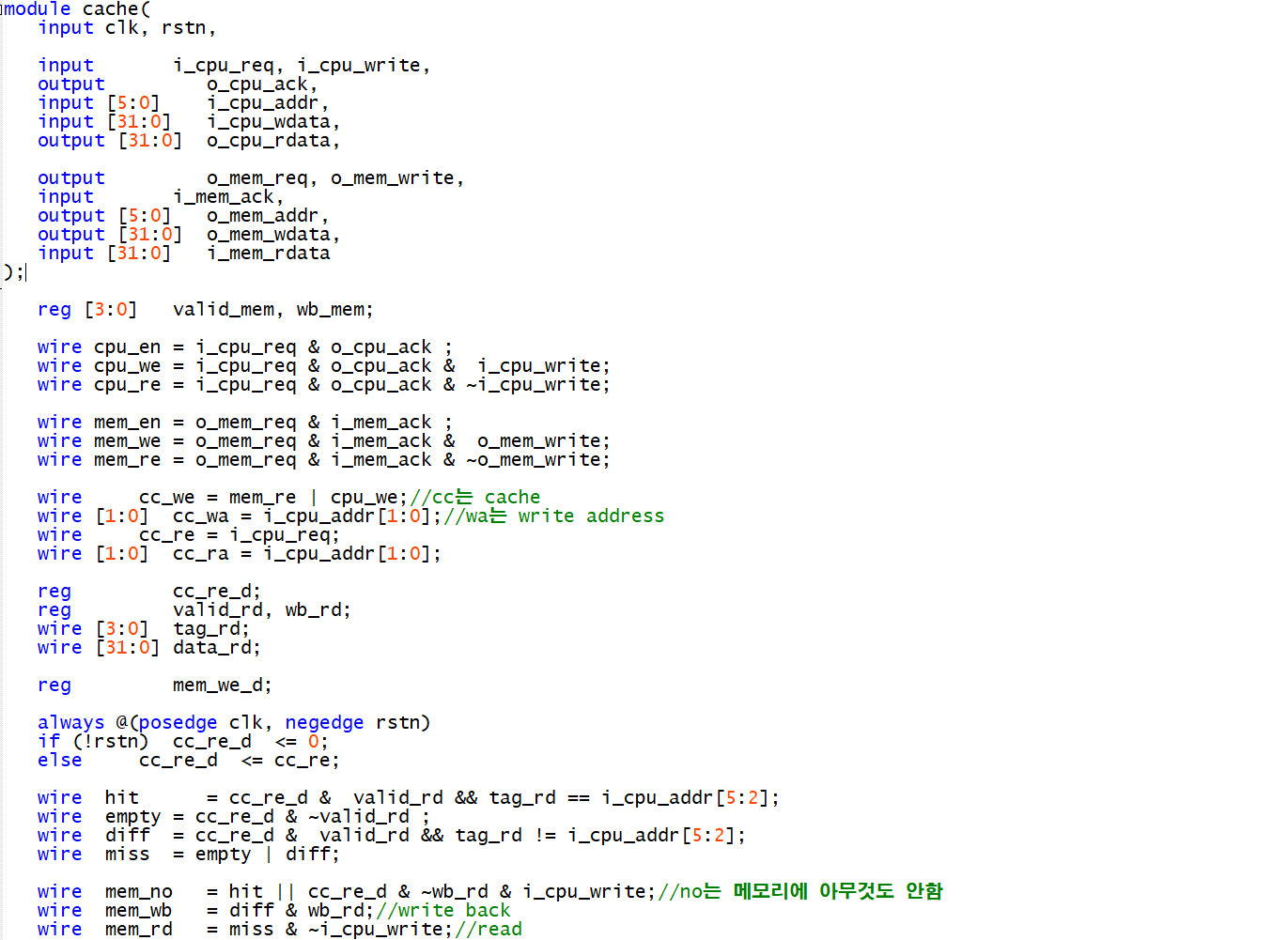

1. CPU - Cache 인터페이스

- i_cpu_req: CPU 요청 신호

- i_cpu_write: CPU 쓰기 요청 신호

- o_cpu_ack: CPU 요청에 대한 Cache 응답

- i_cpu_addr: 6-bit CPU 주소

- i_cpu_wdata: 32-bit CPU 쓰기 데이터

- o_cpu_rdata: 32-bit CPU 읽기 데이터

2. Cache - Memory 인터페이스

- o_mem_req: Memory 요청 신호

- o_mem_write: Memory 쓰기 요청 신호

- i_mem_ack: Memory 응답 신호

- o_mem_addr: 6-bit Memory 주소

- o_mem_wdata: 32-bit Memory 쓰기 데이터

- i_mem_rdata: 32-bit Memory 읽기 데이터

Cache Control Logic

1. Cache Read/Write Enable 신호

- cpu_en: CPU 요청이 활성화되었는지 확인 (i_cpu_req & o_cpu_ack)

- cpu_we: CPU가 데이터를 쓰는 경우 (i_cpu_req & o_cpu_ack & i_cpu_write)

- cpu_re: CPU가 데이터를 읽는 경우 (i_cpu_req & o_cpu_ack & ~i_cpu_write)

- mem_en: Memory 액세스가 이루어지는지 확인 (o_mem_req & i_mem_ack)

- mem_we: Memory 쓰기 동작 여부 (o_mem_req & i_mem_ack & o_mem_write)

- mem_re: Memory 읽기 동작 여부 (o_mem_req & i_mem_ack & ~o_mem_write)

2. Cache Hit & Miss 판별

- hit: Valid한 Cache Line이 있고, Tag가 일치하는 경우

- empty: Valid하지 않은 Cache Line에 접근하는 경우

- diff: Valid하지만 Tag가 일치하지 않는 경우 (Eviction 필요)

- miss: empty 또는 diff가 발생한 경우

Memory Access Control

- mem_no: Cache Hit이거나 Write-Back이 필요 없는 Write Operation → Memory 접근 불필요

- mem_wb: Cache Miss이며 Write-Back이 필요한 경우 → Eviction 발생

- mem_rd: Cache Miss이며 Read Operation → Memory에서 새로운 데이터 로드

Tag & Data Storage

- valid_mem: Valid Bit 저장

- wb_mem: Write-Back이 필요한 Cache Line 여부 저장

- tag_mem: Tag 정보 저장

- data_mem: Cache Data 저장

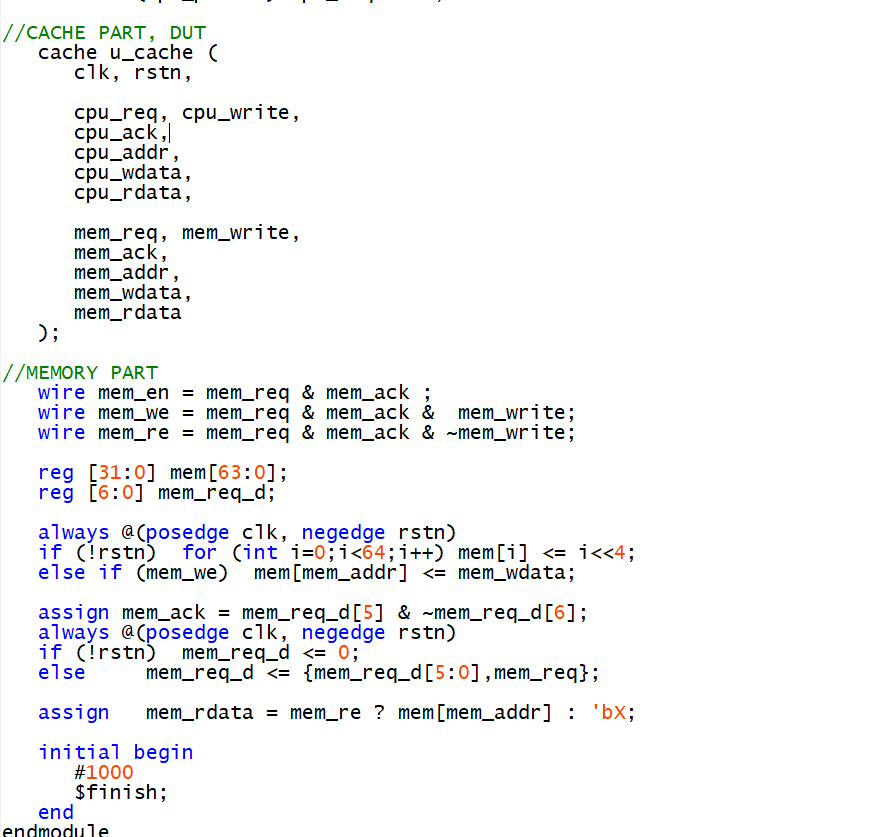

Testbench code

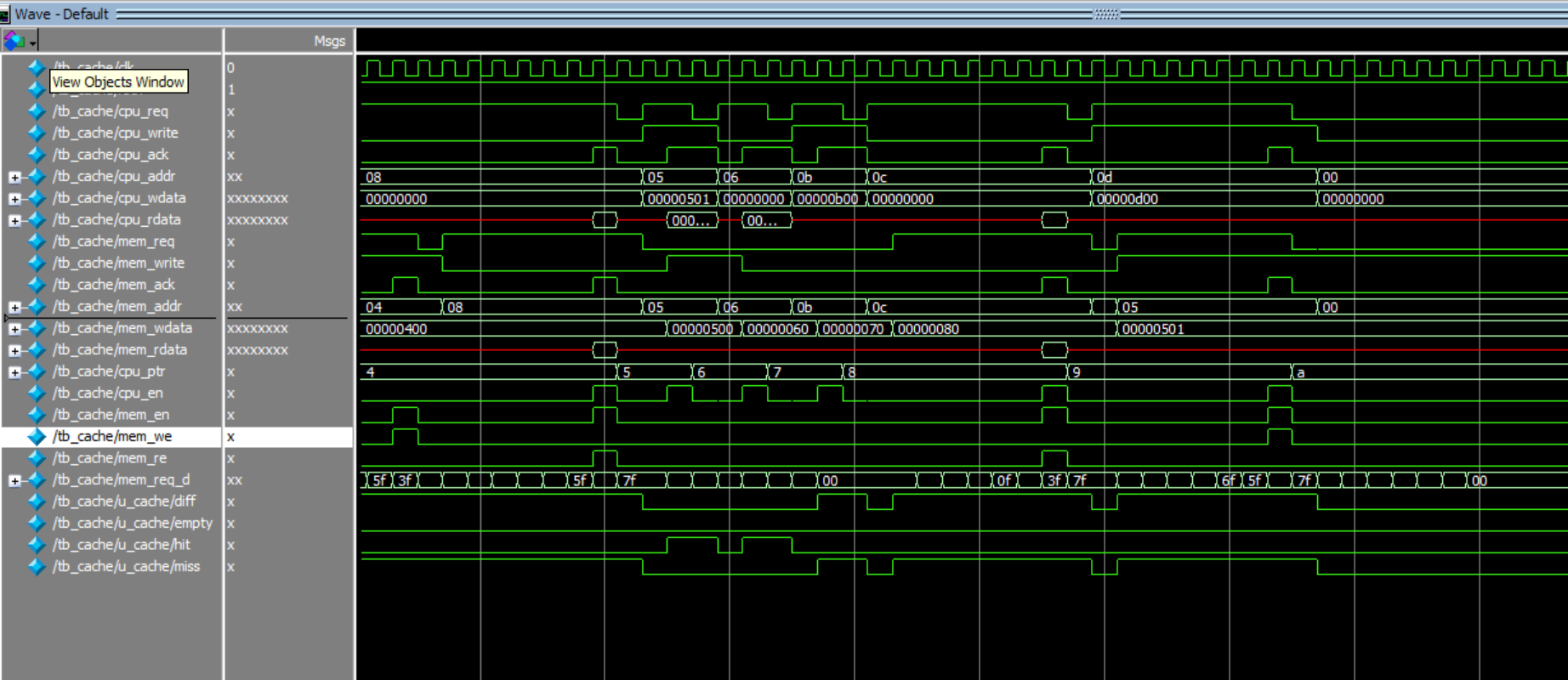

- Clock(clk, 10ns 주기)과 Reset(rstn)을 생성해 동기식 동작을 제어하도록 설계했다.

- 초기 20ns 동안 Reset을 비활성화(rstn=0) 후 30ns에 활성화(rstn=1)로 설정해 Cache와 Memory 초기화를 보장하도록 설계했으며, CPU와 Memory 간 다양한 시나리오를 시뮬레이션하기 위해 10개의 명령(cmd)을 순차적으로 수행하도록 설계했다.

- CPU Part는 Write(ex) 주소 0x04에 0x400 Write)와 Read(ex) 주소 0x06에서 Read)를 통해 Cache Hit, Miss, Write-Back 동작을 테스트하도록 설계했으며, cpu_req, cpu_write, cpu_addr, cpu_wdata 신호를 cache 모듈로 전달하고 cpu_ack, cpu_rdata로 응답을 수신하도록 설계했다.

- Cache DUT는 Memory Request(mem_req, mem_write, mem_addr, mem_wdata)를 생성해 64개 엔트리(각 32비트) Memory(mem)와 통신하도록 설계했으며, Memory는 Clock 기반으로 읽기(mem_re)와 쓰기(mem_we)를 처리하고 mem_ack로 응답을 제어하도록 설계했다.

- 시뮬레이션은 1000ns 후 $finish로 종료되도록 설계하였다