SRAM Architecture, Interface, Protocol

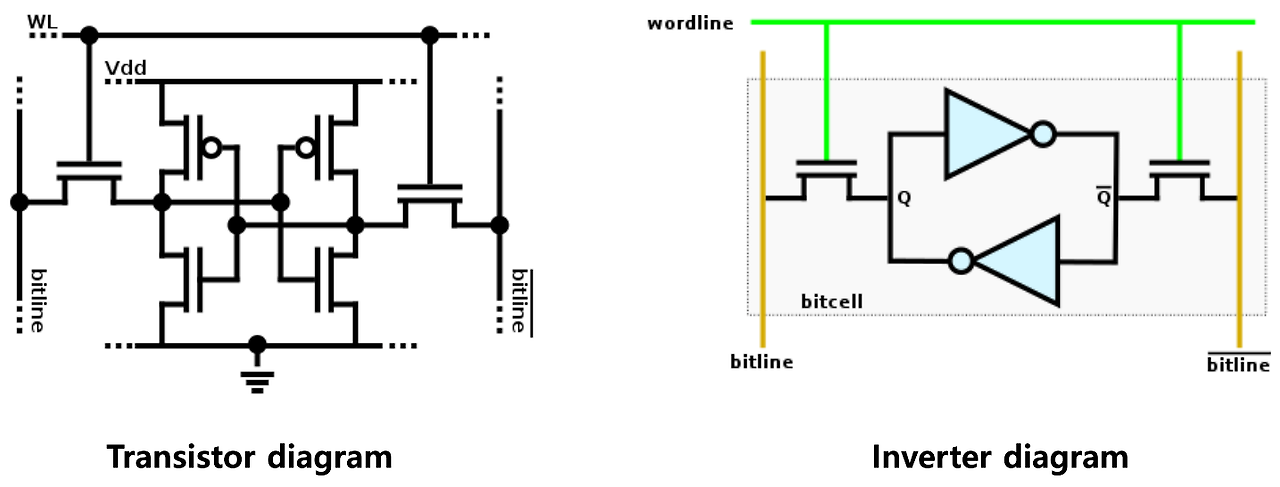

SRAM을 구성하는 cell의 구조를 나타낸 그림이다. 실제 cell은 왼쪽(Transistor diagram) 그림과 같이 6개의 transistor로 구성되는데, 이 구조는 오른쪽의 Inverter diagram과 구조적으로 동일하다. 이 셀은 데이터를 1비트 저장할 수 있다.

- 두 개의 Inverter (4개의 트랜지스터):

- SRAM 셀의 핵심은 두 개의 CMOS 인버터가 서로 교차 연결된 구조

- 각 인버터는 PMOS(풀업)와 NMOS(풀다운) 트랜지스터 한 쌍으로 구성되며 이게 총 4개의 트랜지스터를 차지

- 이 두 인버터가 서로 출력과 입력을 연결해서 플립플롭 구조를 형성하는데 이게 데이터를 안정적으로 저장할 수 있는 이유이다. 이 플립플롭이 Latch의 역할

-

Positive feedback을 통해 Latch의 역할을 함과 동시에 신호를 증폭

-

Latch로 동작해서 한 번 데이터(0이나 1)가 저장되면 전원이 유지되는 한 그 상태를 계속 기억하며 래치가 데이터를 안정적으로 홀드하는 특성 덕분에 SRAM은 리프레시가 필요 없는 정적 메모리가 됨.

- 액세스 트랜지스터 (2개의 트랜지스터):

- 나머지 2개의 NMOS 트랜지스터는 셀에 데이터를 읽거나 쓰기 위해 외부 비트 라인(Bit Line, BL과 BL̅)에 연결

- 이 트랜지스터들은 워드 라인(WL)에 의해 제어되는데 WL이 활성화되면 셀이 비트 라인과 연결돼서 데이터를 읽거나 쓸 수 있게 됨.

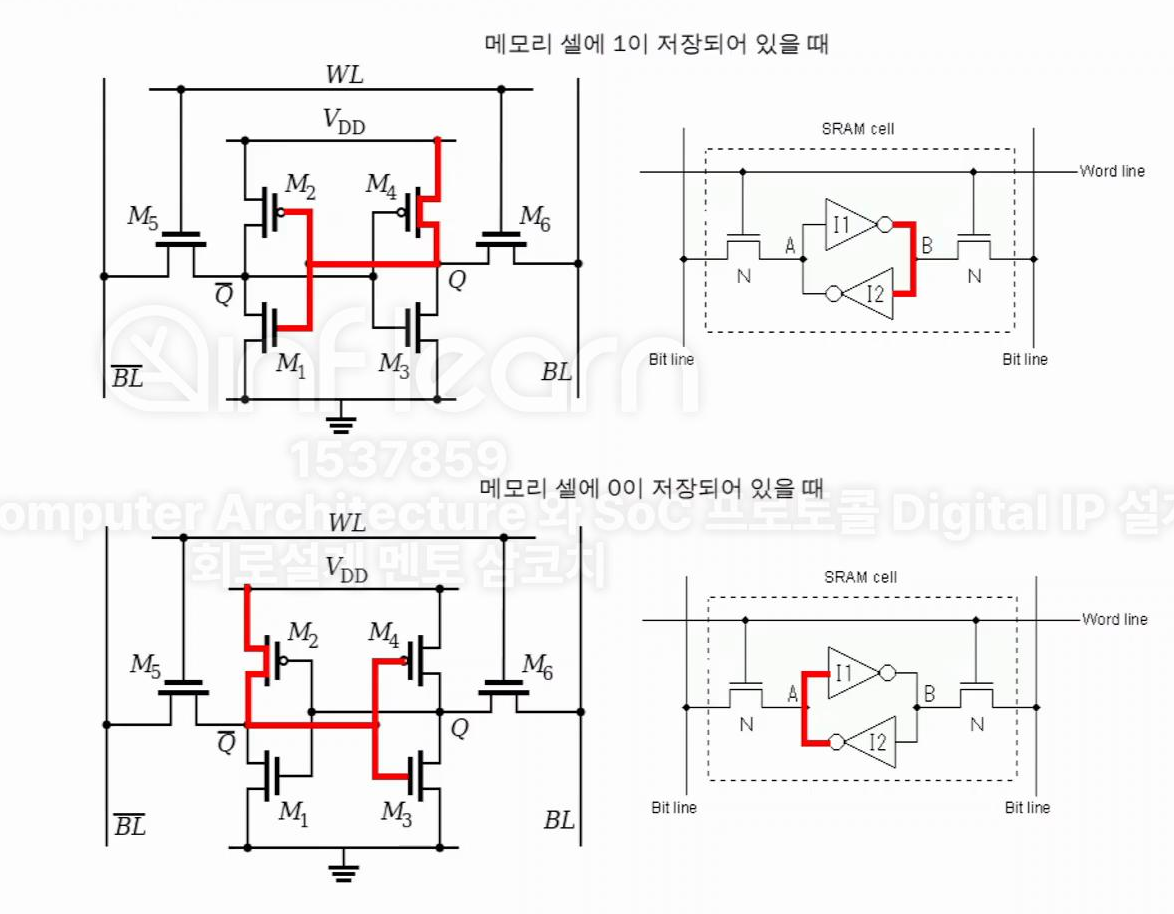

구조를 이해하면 간단하다.

메모리 셀에 1이 저장된 경우에 보면 Vdd에서 M4를 거쳐 High가 들어오면 M1이 on되고 GND가 연결될것이고 이는 LOW신호로 다시 M3로 들어와 M2가 on되어 Vdd가 연결되는 순환구조가 형성된다.

0은 Vdd에서 M2를 거쳐 High가 들어온다고 생각하면 된다.

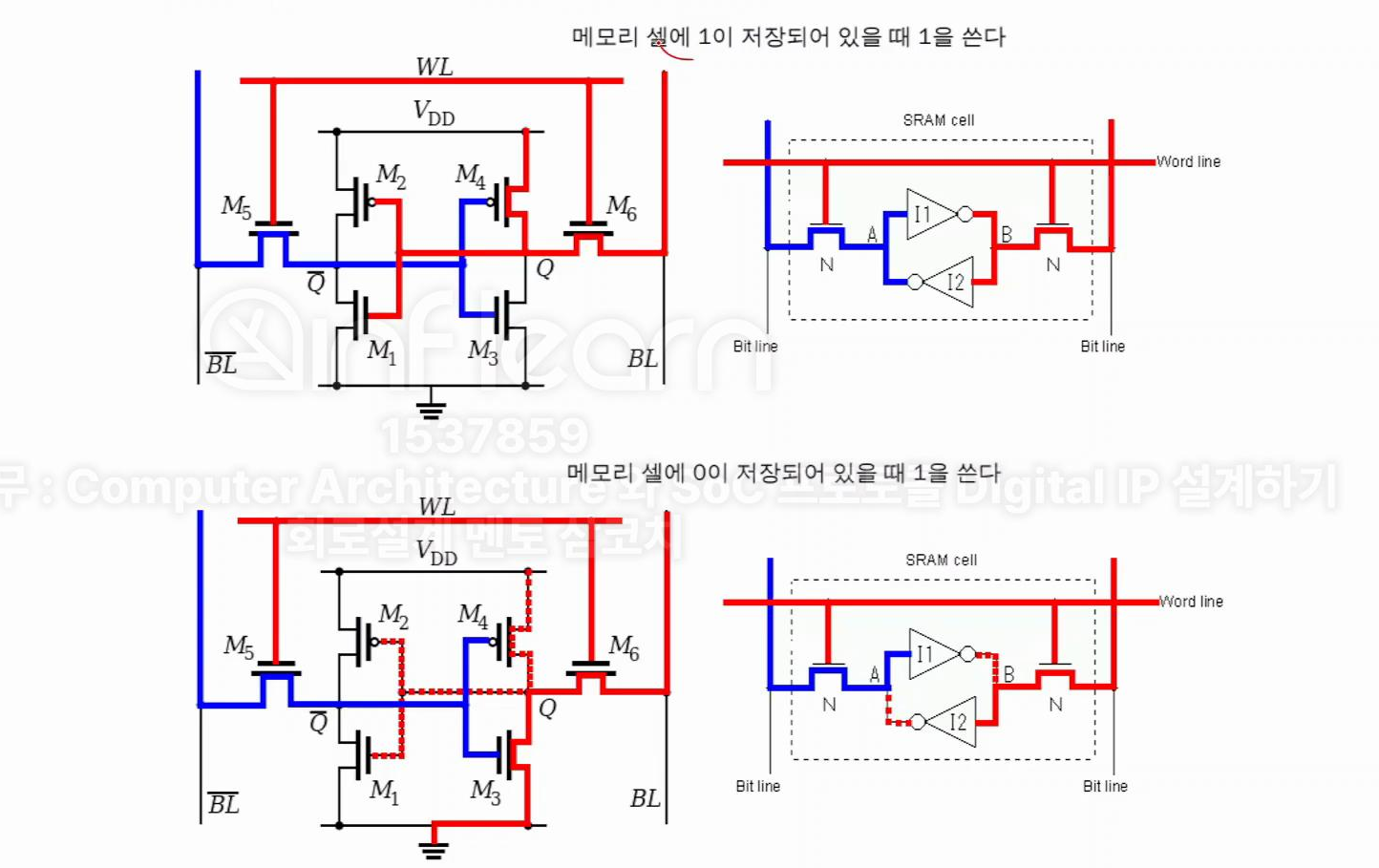

SRAM WRITE

WRITE를 하는 과정을 봐보자. 이때는 BL에서는 어딘가에서 HIGH 전압을 계속 공급해 주고있는 경우이다.

1이저장되어있으면 현재 Inverter 다이어그램을 봤을 떄 원래 A쪽은 Low, B쪽은 High 신호가 걸려있게 된다. BL에서 High가 들어오면 원래 신호 그대로 유지가 된다.

0이 저장되어 있을 때는 A쪽이 High, B쪽이 Low가 되는데 이때 B쪽으로 High 전압이 들어오게 되고 A쪽으론 Low한 신호가 들어오면서 1이 써지게 된다.

SRAM READ

Read를 하는 경우에는 BL에 대해 강력한 전하를 공급해주는 시그널이 없다. 따라서 BL에 High와 Low의 중간정도의 전압을 미리 공급해준다. Precharge해주는 것이다.

'1'이 저장된 경우 (Q = VDD, Q̅ = 0V)

SRAM의 읽기 동작에서 '1'이 저장된 6T 셀의 charge sharing 과정은 word line(WL)이 활성화되어 access transistor(M5, M6)가 켜질 때 시작된다. 셀의 Q 노드가 VDD(ex) 1.8V)로, Q̅ 노드가 0V로 유지되고, bit line(BL, BL̅)은 precharge로 VDD/2(ex) 0.9V)로 초기화된 상태에서, Q가 BL에, Q̅가 BL̅에 연결되면 전하가 재분배된다. Q의 전하(C_cell * VDD)와 BL의 전하(C_bitline * VDD/2)가 합쳐져 새로운 전압을 형성하며, C_cell이 C_bitline보다 훨씬 작으므로 BL은 VDD/2보다 약간 상승(예: 1.0~1.2V)하고, Q̅(0V)가 BL̅(VDD/2)에 연결되면서 BL̅은 약간 하락(예: 0.7~0.8V)한다. 이로 인해 BL과 BL̅ 간에 미세한 전압 차이(수 mV)가 발생하며, 이 차이는 sense amplifier에 의해 증폭되어 '1'로 판별된다.

'0'이 저장된 경우 (Q = 0V, Q̅ = VDD)

SRAM의 읽기 동작에서 '0'이 저장된 6T 셀의 charge sharing 과정은 word line(WL) 활성화로 시작되며, Q 노드가 0V로, Q̅ 노드가 VDD로 유지되고, bit line(BL, BL̅)이 VDD/2로 precharge된 상태에서 진행된다. Q가 BL에, Q̅가 BL̅에 연결되면, Q(0V)의 전하가 BL(VDD/2)와 재분배되며 BL의 전압은 0V와 VDD/2 사이로 약간 하락(예: 0.8~0.9V)하고, Q̅(VDD)의 전하가 BL̅(VDD/2)와 합쳐져 BL̅의 전압은 VDD와 VDD/2 사이로 약간 상승(예: 1.0~1.1V)한다. 이 전하 재분배는 C_cell이 C_bitline보다 훨씬 작아 미세한 전압 차이(수 mV)를 생성하며, BL과 BL̅ 간의 차이는 sense amplifier에 의해 증폭되어 '0'로 판별된다.

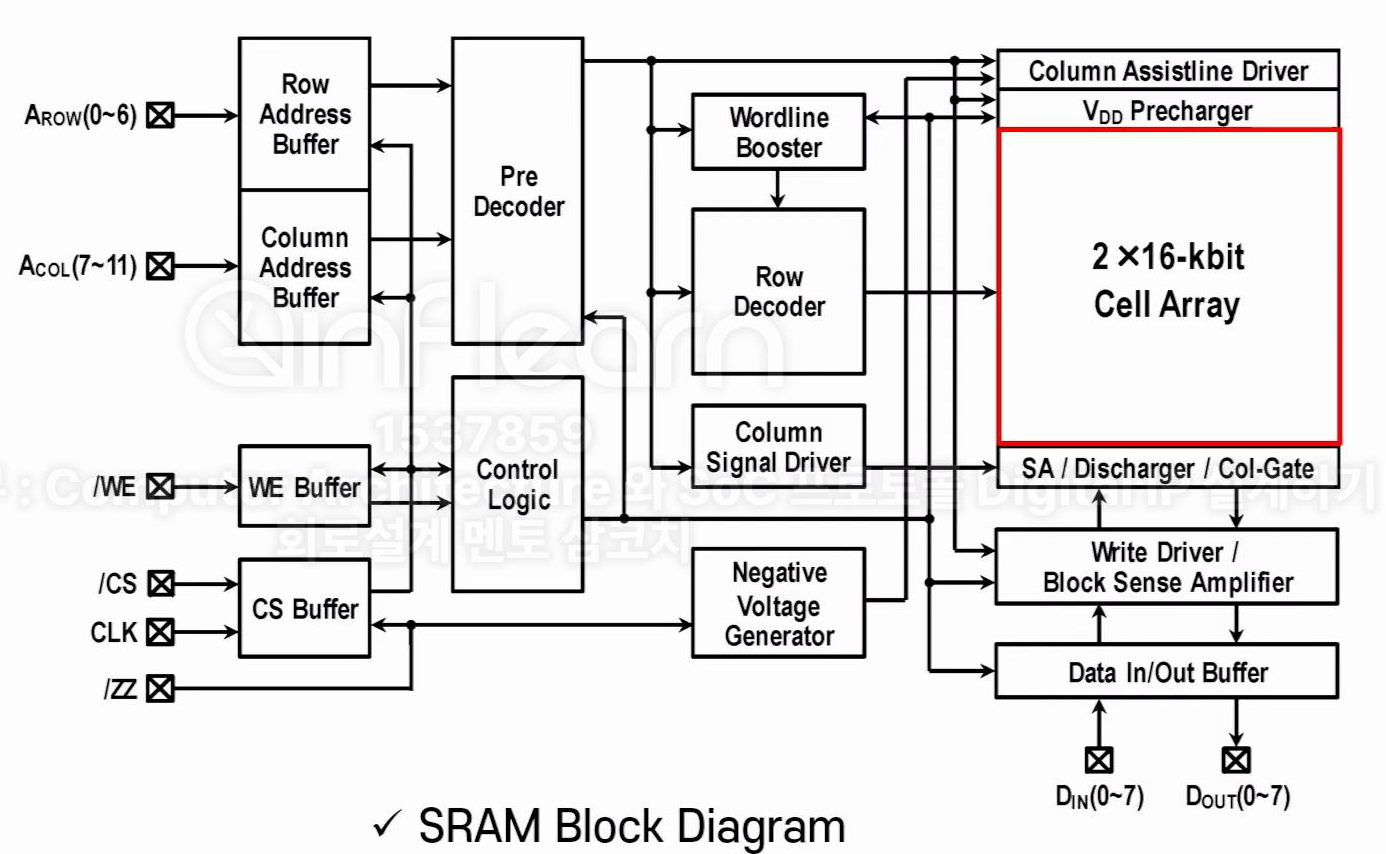

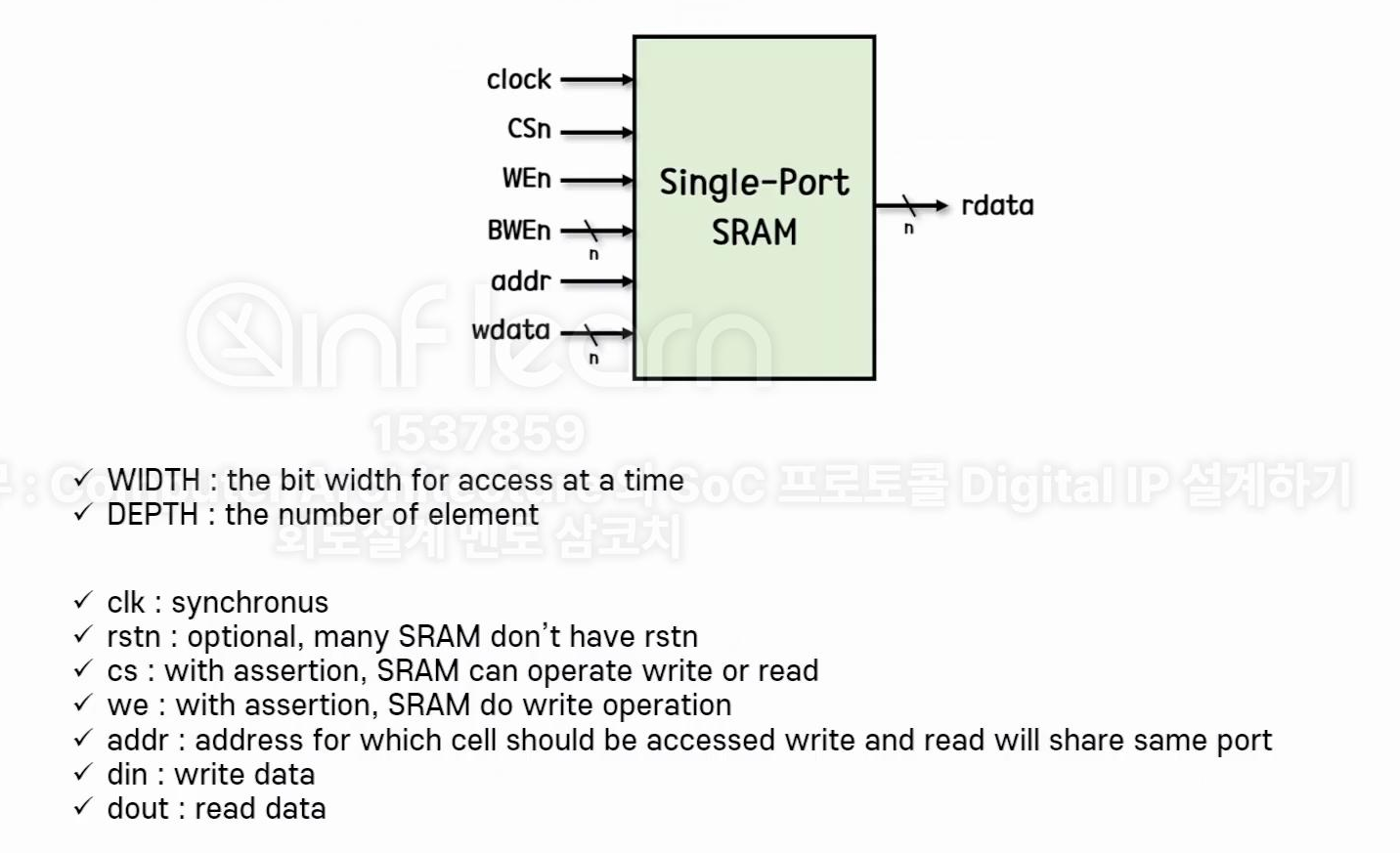

SRAM Block Diagram

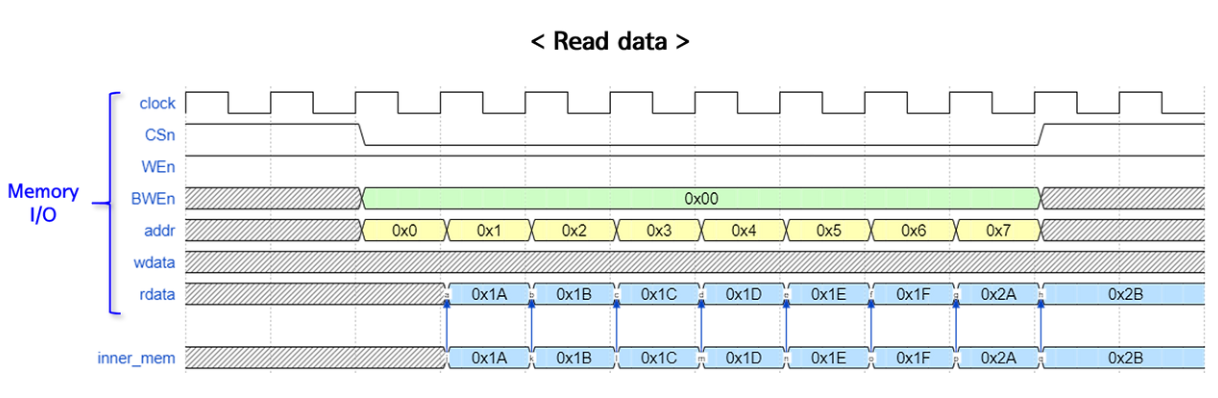

메모리 프로토콜

위의 예시에서는 address를 1씨 순차적으로 증가시키며 메모리에 데이터를 입력함.

메모리를 선택하기 위해 CSn(Chip select, n이 붙어있으므로 0일때 동작)이 0으로 깔렸으며 이때 addr이 바로 들어옴.

WEn(Write Enable, n이붙어있으므로 0일때 동작)이 들어오므로 wdata(Wrtie data)를 inner_mem으로 한클럭 밀려서

입력하고 있음.

write랑 비슷한 구조인데, read를 하는 것이기 때문에 WEn은 1로 유지. 한 클럭마다 inner_mem에 대한 데이터가 rdada로 바로 읽어오게 됨. write처럼 delay되지 않음.