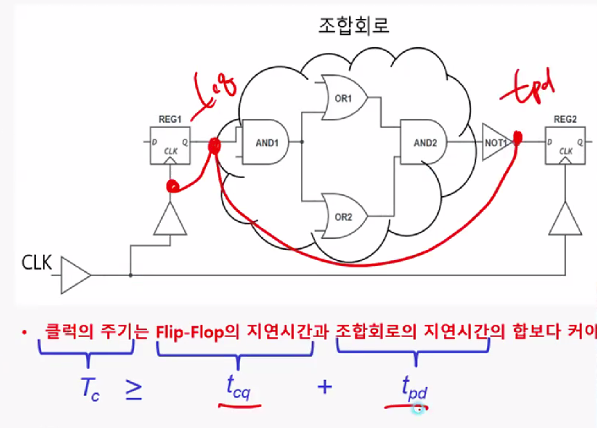

13.1 정적 타이밍 분석(STA), 동적 규율(Dynamic Discipline)

타이밍 조건

회로가 올바르게 동작하기 위해 신호가 레지스터와 조합회로 사이에서 지켜야하는 최소 및 최대 시간 제약

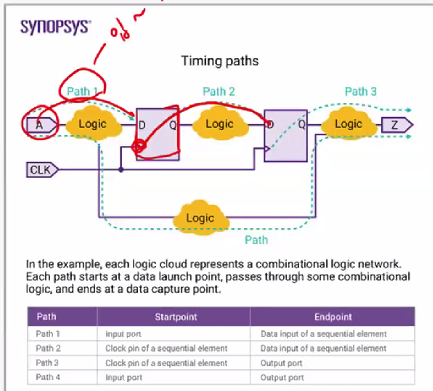

디지털 회로에는 레지스터와 레지스터 간의 경로뿐 아니라, 다양한 타이밍 경로 존재

- path1: 입력 포트로 들어온 신호가 조합 회로를 거쳐 레지스터의 입력단에 도달하는 경로

- path2: 레지스터의 클럭 입력단->조합회로->레지스터 입력단

- paht3: 레지스터의 클럭 입력단->조합회로->출력포트

- path4: 레지스터 통과 X, 입력포트->조합회로->출력포트

정적 타이밍 분석(Static Timing Analysis)

- 디지털 회로 내에 모든 가능한 경로에서 타이밍 위반이 있는지 확인하여 성능 검증

- 회로의 모든 경로에 대해 입력 신호와는 무관하게 지연시간을 계산

- 시뮬레이션 없이 수학적 분석을 통해 이루어짐

동적 타이밍 분석

- 실제 입력 신호를 사용하여 회로를 시뮬레이션하고 특정 입력 조건에서의 타이밍 성능 확인

- 정적 시간 분석보다 분석에 더 많은 시간 소요

플립플롭의 동적규율(Dynamic Discipline)

D플립플롭에 대해 타이밍 조건을 알아보자

- D플립플롭의 동작 : 클럭신호가 상승에지(또는 하강에지)일 때, D 입력에 있는 값이 샘플링되어 플립플롭 내부에 저장되며 저장된 값은 즉시 Q출력으로 전달

- 이후 클럭의 에지가 다시 발생하기 전까지 Q출력은 변하지 않고 저장된 값을 유지

- 다음 클럭 에지에서 다시 D값을 샘플링하고 이를 출력 Q에 반영

- 플립플롭은 항상 클럭신호의 에지에서 D입력을 샘플링하므로 D입력은 클럭 신호의 에지 발생 전후로 일정한 값을 유지

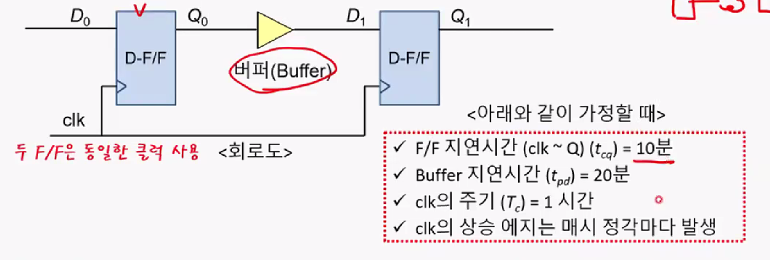

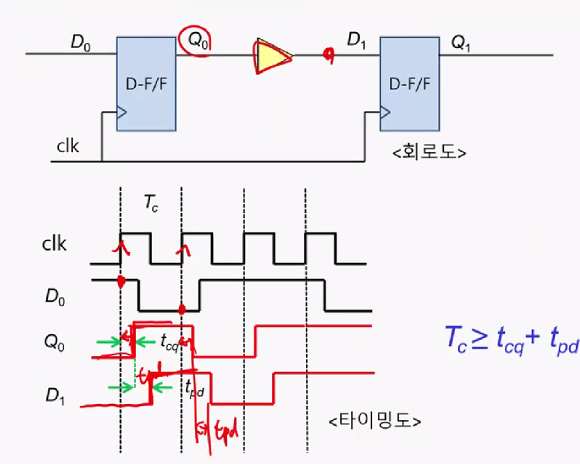

모든 D-F/F들이 0으로 초기화 되어있고 1시30분에 D0에 '1'이도착한다면

- Q0는 언제 1이 되는가? 2:10

- D1은 언제 1이되는가? 2:30

- Q1은 언제 1이 되는가? 3:10

- 클럭 주기를 줄일수 있는가? 그렇다면 Tc의 최소값은? 30분

- 클럭의 주기는 Flip-Flop의 지연시간과 조합회로의 지연시간이 합보다 커야함.

- Tc >= t(cq) + t(pd)

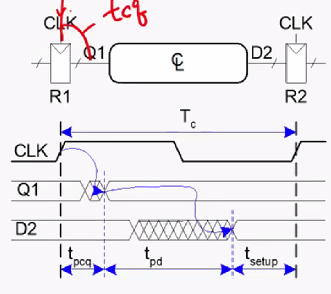

셋업 타임(setup time)조건: 입력신호 D가 크럭의 에지 발생 전 일정 시간동안 안정된 상태로 유지되어야한다

홀드타임(hold time)조건 : 클럭의 에지가 발생한 후에도 일정 시간동안 입력신호가 안정된 상태로 유지되어야 한다.

- 이를 만족하지 못한다면 플립플롭은 일시적으로 안정된 0 또는 1 상태에 도달하지 못함.

- 이 경우 불안정한 상태에 머무르다 안정된 상태가 되긴 하나 이 과정에서 신호 처리 지연이나 오류 발생

- 메타안정상태(metastability):타이밍 위반으로 인해 플립플롭이 일시적으로 빠지게 되는 불안정한 상태

- 플립플롭의 동적 규율: 플립플롭이 메타안정상태에 빠지는 것을 막기 위해 모든 플립플롭은 셋업타임 ㅈ건과 홀드 타임 조건을 준수해야함.

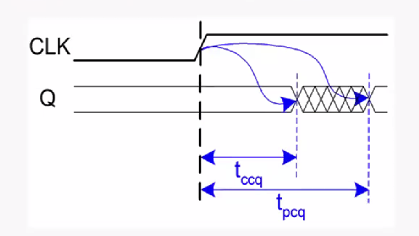

플립플롭 전파지연(propagation delay) : 클럭의 에지가 발생한 후, 플립플롭의 입력 D가 출력 Q로 전달하는데 걸리는 최대 지연시간

플립 플롭 오염지연(contamination delay) : 클럭의 에지가 발생한 후, 플립플롭의 입력 D가 출력 Q로 전달하는데 걸리는 최소 지연시간

조합회로의 전파지연: 출력이 입력 변화에 맞춰 완전히 바뀌기까지 발생하는 최대 지연시간

조합회로의 오염지연: 입력이 변화했을 때 출력이 가장 빠르게 변화하기 시작하는 시점까지 걸리는 최소 지연 시간

- Tc >= t(pcq) + t(pd) + t(setup)

- tpcq, tsetup은 제조사에 의해 주어짐

- tpd를 줄여야함.

- t(ccq) + t(cd) >= t(hold)

- tcd>= t(hold) - t(ccq)

- t(hold), t(ccq)는 제조사에 의해 주어짐

- 설계자는 t(cd)를 늘려 식이 만족되도록 설계

STA에서 검증해야하는 path: A~X, A~Y, B~X, B~Y, C~X, C~Y, D~Y

최대 지연 시간: A~Y or B~Y

t(pd)=3x40ps = 120ps

셋업타임 조건:

- Tc>=(80+120+50)ps = 250ps

- fc = 1/Tc<=4.0GHz

최소 지연 시간: C~X or D~Y

t(cd) = 25ps

홀드타임 조건:

- tccq+tcd>=t(hold)

- (30+25)ps>=60ps 지금 조건으로는 홀드 타임 조건이 충분하지 않음.

짧은 경로에 버퍼 추가

(30+50)ps >=60ps가 되었으므로 홀드타임 조건 만족.

클럭의 불확실성(Clock uncertainty)

- 클럭 신호가 이상적인 시점에 도착하지 않고 예상보다 빠르거나 느리게 도착할 수 있는 시간 변동

- 클럭 스큐, 지터, 타이밍 마진

- Jitter: 이상적인 클럭 주기에서의 시간 변동, 신호의 주파수 안정성과 타이밍 저하

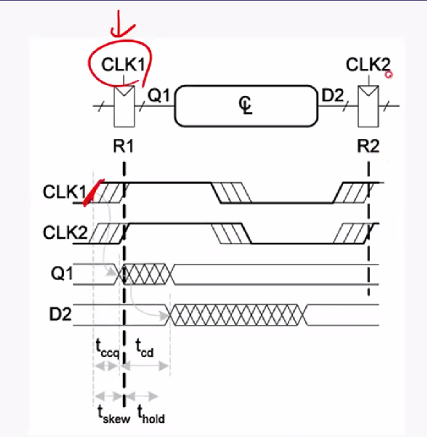

클럭 스큐(skew): 동일한 클럭 신호가 서로 다른 위치에 있는 플립플롭들에 전달될 때 발생하는 시간차이

클럭이 한 플립플롭에 도달하는 시점과 다른 플립플롭에 도달하는 시점이 미세하게 달라질 수 있음.(이는 잘못 샘플링 되거나 타이밍 오류 유발)

클럭의 스큐를 고려하면 셋업 타임 조건과 홀드타임 조건 수식을 변경해야함

스큐에 의한 셋업타임 조건

- CLK2가 CLK1보다 빠르게 도착

- Tc>=T(pcq) + t(pd) + t(setup) + t(skew)

스큐에 의한 홀드타임 조건

- CLK2가 CLK1보다 느리게 도착

- t(ccq)+ t(cd) >= t(hold) + t(skew)